# NATIONAL SECURITY AGENCY CENTRAL SECURITY SERVICE FORT GEORGE G. MEADE, MARYLAND

TM 11-5895-821-14-1 TO 3IS5-2FYC12-1 NAVELEX 0967-LP-544-7010 TEMO-888-010A

A N / F Y C - 1 2

DIGITAL DATA SET

O P E R A T I O N A N D M A I N T E N A N C E

# MANUAL

**VOLUME 1 OF 2**

**OCTOBER 1975**

#### INTRODUCTION

This manual provides installation, operation and maintenance instructions for the Digital Data Set AN/FYC-12. In addition, it contains principles of operation and illustrated parts breakdown chapters as supplementary technical information for maintenance purposes. This manual is divided into two volumes.

Volume I contains the following:

| Chapter | 1 | Description of Equipment |

|---------|---|--------------------------|

| Chapter | 2 | Installation             |

| Chapter | 3 | Operating Instructions   |

| Chapter | 4 | Principles of Operation  |

| Chapter | 5 | Preventive Maintenance   |

| Chapter | 6 | Corrective Maintenance   |

Volume II contains the following:

| Chapter 7 | Illustrated Parts Breakdown  |

|-----------|------------------------------|

| Appendix  | (Maintenance Illustrations ) |

The Digital Data Set AN/FYC-12 Technical Manual has been written for cryptologic technicians whose technical education competence shall equal that of a graduate of a military service school course in electronics of no less than 40 weeks duration.

ANIFYC-12

THIS PAGE INTENTIONALLY LEFT BLANK

# TABLE OF CONTENTS

#### CHAPTER 1

# DESCRIPTION OF EQUIPMENT

| Section |                                     | Paragraph | Page  |

|---------|-------------------------------------|-----------|-------|

| I.      | CLASSIFICATION                      |           |       |

|         | Classification of Equipment         | 1-1       | 1-1   |

| II.     | GENERAL DESCRIPTION                 |           |       |

| 11.     | Purpose of Equipment                | 1 - 2     | 1-1   |

|         | Functional Description              | 1 - 3     | 1-1   |

|         | System Operation                    | 1 - 3 a   | 1-1   |

|         | Summary of Capabilities             | 1 - 3 b   | 1-3   |

|         | Physical Description                | 1 - 4     | 1-3   |

|         | Steel Cabinet Assembly Al           | 1-4a      | 1-4   |

|         | Electronic Chassis Assembly A2      | 1 - 4 b   | 1 - 4 |

|         | Equipment Required But Not Supplied | 1 - 5     | 1 - 6 |

|         | Equipment Identification            | 1 - 6     | 1 - 6 |

|         | Electrical Characteristics          | 1 - 7     | 1 - 6 |

|         | DC Input Power Required             | 1 -7a     | 1 - 6 |

|         | Line Signals                        | 1 - 7 b   | 1 - 7 |

|         | Input Signals                       | 1 - 7 c   | 1 - 7 |

|         | Output Signals                      | 1 - 7 d   | 1 - 7 |

|         | Environment                         | 1 - 8     | 1-13  |

|         | CHAPTER 2                           |           |       |

|         | INSTALLATION                        |           |       |

| I.      | UNPACKING AND INSPECTION            |           |       |

| 1.      | Packaging Data                      | 2 - 1     | 2 - 1 |

|         | Unpacking                           | 2 - 2     | 2 - 1 |

|         | Inspection Procedure                | 2 - 3     | 2 - 1 |

|         | Damage Report                       | 2 - 4     | 2 - 2 |

| II.     | INSTALLATION PROCEDURE              |           |       |

|         | General                             | 2 - 5     | 2 - 2 |

|         | Tools and Test Equipment            | 2 - 6     | 2 - 2 |

|         | Locating the Equipment              | 2 - 7     | 2 - 2 |

# AN/FYC-12

## UNCLASSIFIED

| Section |                                           | <u>Paragraph</u> | Page           |

|---------|-------------------------------------------|------------------|----------------|

|         | Equipment Mounting                        | 2 - 8            | 2 - 2          |

|         | Cable Fabrication                         | 2 - 9            | 2 - 2          |

|         | Signal Cable                              | 2 - 9 a          | 2 - 4          |

|         | Check For Correct Connections             | 2 - 9 b          | 2 - 7          |

| III.    | ADJUSTMENTS                               |                  |                |

|         | Line Driver Capacitor Selection           | 2 - 10           | 2 - 7          |

|         | Transmit Inhibit Option                   | 2-11             | 2 - 9          |

|         | Memory Length Selection                   | 2 - 12           | 2 - 11         |

|         | Selection of Data Format                  | 2-13             | 2-15           |

|         | Center Sampling                           | 2 - 1 4          | 2-16           |

|         | Operation of Center Sample Switch         | 2 - 1 4 a        | 2-16           |

|         | Adjustment of Center Sample Switch        | 2 - 14 b         | 2-17           |

|         | Installation Tests                        | 2 - 1 5          | 2-19           |

| IV.     | PACKING AND STORAGE                       |                  |                |

|         | Packing Procedures                        | 2-16             | 2-19           |

|         | Storage                                   | 2-17             | 2-19           |

|         | CHAPTER 3                                 |                  |                |

|         | OPERATING INSTRUCTIONS                    |                  |                |

| I.      | CONTROLS AND INDICATORS                   |                  |                |

|         | Identification of Controls and Indicators | 3-1              | 3-1            |

| II.     | OPERATING PROCEDURES                      |                  |                |

|         | Turn On Procedure                         | 3 - 2            | 3 - 4          |

|         | Pre-Operational Procedures                | 3 - 3            | 3 - 7          |

|         | Operating Procedures                      | 3 - 4            | 3 - 7          |

|         | Shut Down Procedure                       | 3 - 5            | 3 - 7          |

|         | CHAPTER 4                                 |                  |                |

|         | PRINCIPLES OF OPERATION                   |                  |                |

| I.      | BASIC PRINCIPLES                          |                  |                |

| 1.      | General                                   | 4 - 1            | 4 - 1          |

|         | Definitions                               | 4 - 1            | 4 - 1<br>4 - 1 |

|         | Delimitions                               | 4-2              | 4-1            |

| Section | <u>P</u>                                     | aragraph_ | Page    |

|---------|----------------------------------------------|-----------|---------|

|         | TTL Logic Modules                            | 4 - 2 a   | 4 - 1   |

|         | Constant Ratio Modes                         | 4 - 2 b   | 4 - 3   |

|         | Supervisory Characters                       | 4 - 2 c   | 4 - 4   |

|         | Input Data Formats                           | 4 - 2 d   | 4 - 5   |

|         | Unused Constant Ratio Codes                  | 4 - 2 e   | 4 - 6   |

|         | ARQ Cycle                                    | 4 - 2 f   | 4 - 6   |

|         | SYNC Cycle                                   | 4 - 2 g   | 4 - 6   |

|         | Rates and Clocks                             | 4 - 2 h   | 4 - 7   |

| II.     | SYSTEM OPERATION                             |           |         |

|         | Initialization                               | 4 - 3     | 4 - 32  |

|         | Transmitter Logic                            | 4 - 3 a   | 4 - 32  |

|         | Receiver Logic                               | 4 - 3 b   | 4 - 32  |

|         | Data Flow                                    | 4 - 4     | 4 - 32  |

|         | Transmitter Step Clock                       | 4 - 4 a   | 4 - 33  |

|         | Receiver                                     | 4 - 4 b   | 4 - 3 3 |

|         | Number of Constant Ratio Codes               | 4 - 4 c   | 4 - 3 4 |

|         | Time For Each Character                      | 4 - 4 d   | 4 - 34  |

|         | ARQ Cycle                                    | 4 - 5     | 4 - 34  |

|         | The Distant Transmitter                      | 4 - 5 a   | 4 - 3 5 |

|         | The Local Transmitter                        | 4 - 5 b   | 4 - 3 5 |

|         | The Distant Receiver                         | 4 - 5 c   | 4 - 3 5 |

|         | Leaving the ARQ Sequence                     | 4 - 5 d   | 4 - 3 6 |

|         | SYNC Cycle                                   | 4 - 6     | 4 - 3 6 |

|         | Initiation of the Resynchronization Sequence | e 4-6a    | 4 - 37  |

|         | The Distant Receiver                         | 4 - 6 b   | 4 - 37  |

|         | The Distant Transmitter                      | 4 - 6 c   | 4 - 37  |

|         | Sync Cycle Indicators                        | 4 - 6 d   | 4 - 3 9 |

|         | Inhibit Operation                            | 4 - 7     | 4 - 39  |

| III.    | UNIT OPERATION                               |           |         |

|         | Initialization                               | 4 - 8     | 4 - 39  |

|         | Transmitter Logic                            | 4 - 8 a   | 4 - 39  |

|         | Receiver Logic                               | 4 - 8 b   | 4 - 42  |

|         | Data Flow                                    | 4 - 9     | 4 - 42  |

|         | Incoming Data                                | 4 - 9 a   | 4 - 43  |

|         | Transmitted Supervisory Control Character    | s 4-9b    | 4 - 4 3 |

|         | Distant Transmitter Inhibit                  | 4 - 9 c   | 4 - 4 4 |

|         | System Memory                                | 4 - 9 d   | 4 - 4 4 |

|         | Parallel -To-Serial Conversion               | 4 - 9 e   | 4 - 4 4 |

|         | Resynchronization                            | 4 - 9 f   | 4 - 4 4 |

|         | Data Transmission                            | 4 - 9 g   | 4 - 4 5 |

#### UNCLASSIFIED

| Section                                | Paragraph            | Page    |

|----------------------------------------|----------------------|---------|

| Transmitter Indicators                 | 4 - 9 h              | 4 - 4 5 |

| Data Reception                         | 4 - 9 i              | 4 - 4 5 |

| Receiver Test Modes                    | 4 - 9 j              | 4 - 45  |

| Normal Data Flow                       | 4 - 9 k              | 4 - 46  |

| Unused Constant Ratio Codes            | 4 - 9 1              | 4 - 46  |

| Invalid Constant Ratio Codes           | 4 - 9 m              | 4 - 47  |

| Received Supervisory Control Charact   | ers 4-9n             | 4 - 47  |

| Cons tan t Ratio Codes Decoding        | 4 - 9 o              | 4 - 47  |

| Serial Data Transmission               | 4 - 9 p              | 4 - 48  |

| Data Flow Inhibit                      | 4 - 9 q              | 4 - 48  |

| Data Timing                            | 4 - 9 r              | 4 - 48  |

| Receiver Indicators                    | 4 - 9 s              | 4-48    |

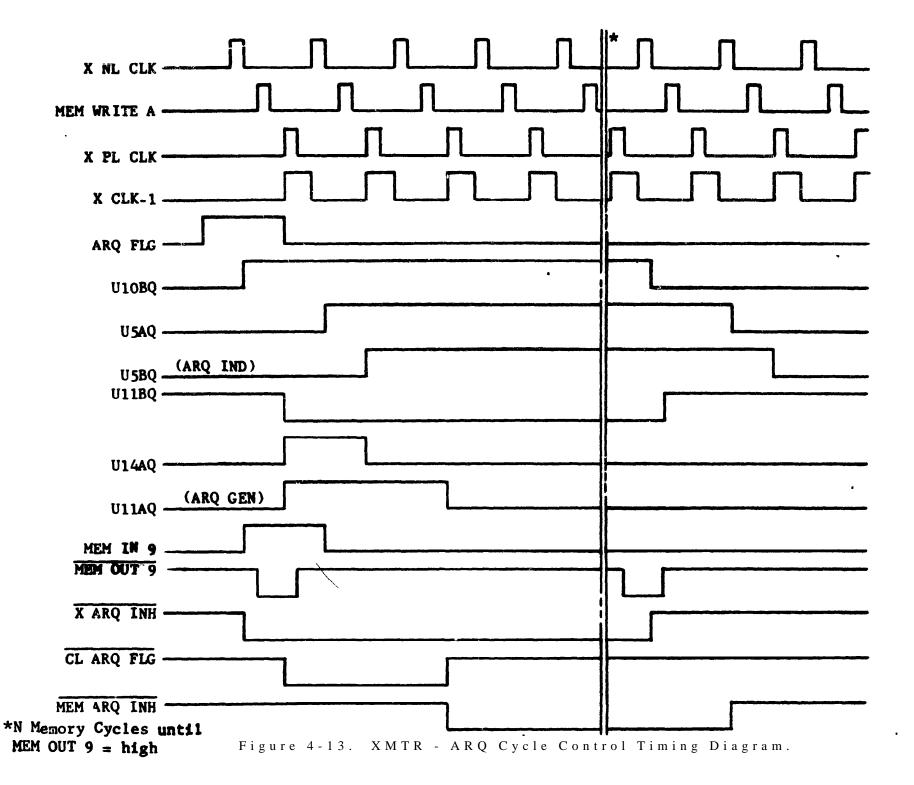

| ARQ Cycle                              | 4 - 10               | 4 - 48  |

| ARQ Initiation                         | 4 - 10a              | 4-49    |

| Setting the ARQ Flag                   | 4 - 10 b             | 4-49    |

| Transmission Response To The ARQ F     | <sub>lag</sub> 4-10c | 4 - 50  |

| Transmitter Character Counter          | 4 - 10 d             | 4 - 50  |

| Retransmission From Memory             | 4 - 10 e             | 4-51    |

| Return To Normal Data Flow             | 4 - 1 0 f            | 4-51    |

| Synchronization Cycle                  | 4 - 11 -             | 4 - 52  |

| Initiation By Operator                 | 4-11a                | 4 - 52  |

| Initiation By Receiver Flag            | 4 - 1 1 b            | 4 - 52  |

| Character Count By Incrementing Mem    | ory 4-11c            | 4-53    |

| Receiver Synchronization               | 4 - 1 1 d            | 4 - 5 4 |

| Return To ARQ Cycle                    | 4 - 11 e             | 4 - 5 4 |

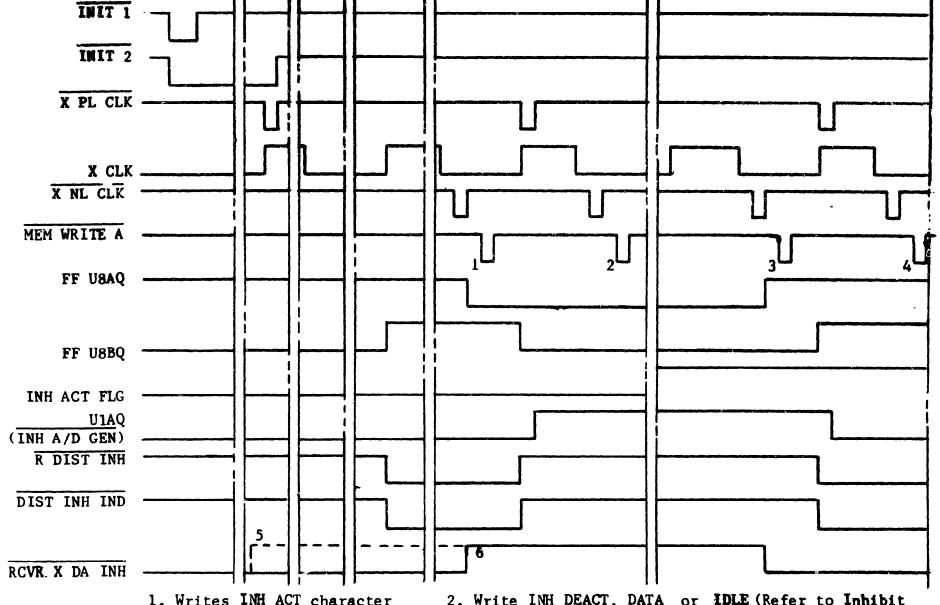

| Inhibit Operation                      | 4 - 1 2              | 4 - 5 4 |

| Generation of Inhibit Supervisory Char | racter 4-12a         | 4 - 5 4 |

| Reception of Inhibit Supervisory Chara | acters 4-12b         | 4 - 5 5 |

| Transmission Response To Receiver F    | Flag 4-12c           | 4 - 5 6 |

| Return To Normal Data Flow             | 4 - 1 2 d            | 4 - 5 6 |

| Power Distribution                     | 4 - 1 3              | 4 - 5 6 |

| Voltages                               | 4-13a                | 4-56    |

| Distribution                           | 4 - 13 b             | 4 - 5 6 |

| Grounding                              | 4-13 c               | 4-56    |

| IV. CIRCUIT DESCRIPTION                |                      |         |

| Transmitter                            | 4 - 1 4              | 4 - 57  |

| A2A8 Level Converter                   | 4 - 1 4 a            | 4-59    |

| A2A1 Data Sample Generator             | 4 - 1 4 b            | 4-61    |

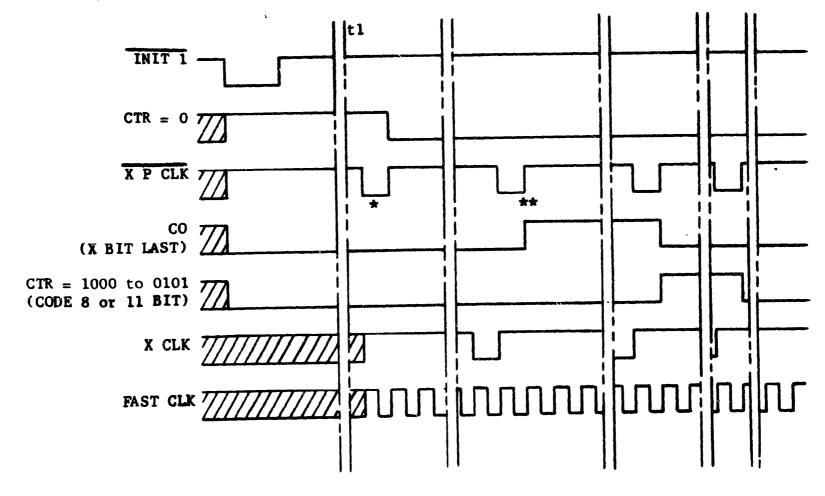

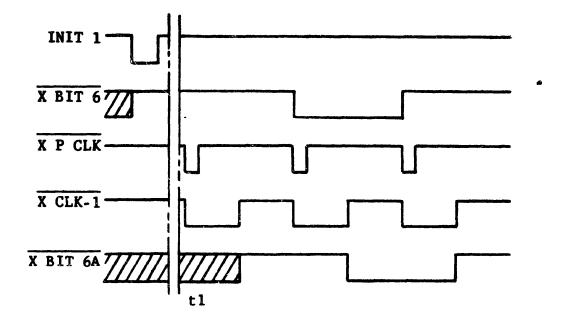

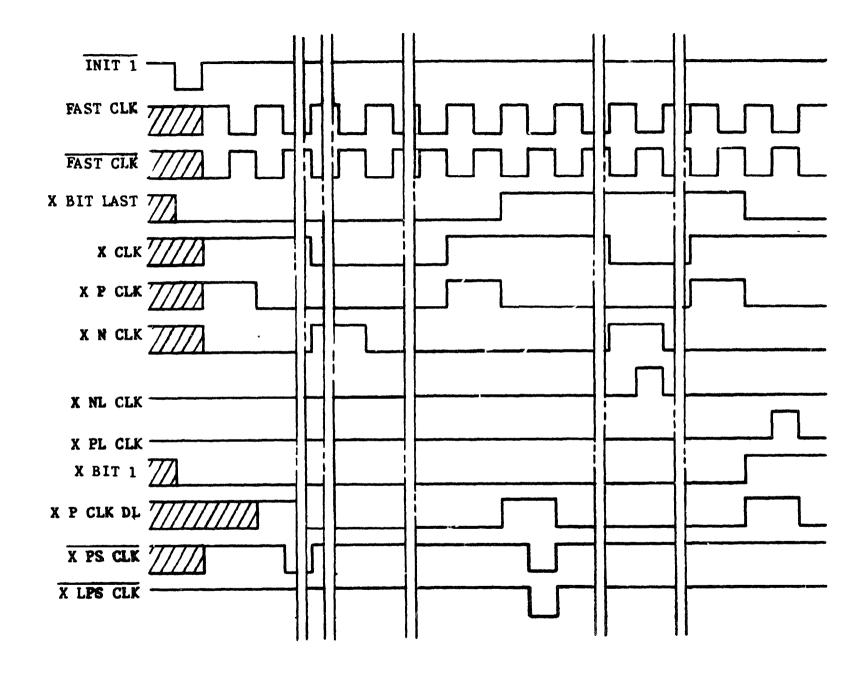

| A 2A2 Fast Clock Step Generator        | 4 - 1 4 c            | 4 - 67  |

| A2A3 Inhibit Control XMTR Clock Ge     | nerator 4-14d        | 4-73    |

| A2A4 XMTR ARQ and Sync Control         | 4 - 1 4 e            | 4-85    |

| A2A5 Constant Ratio Code Generator     | 4 - 1 4 f            | 4 - 9 5 |

| Section |                                                                                                                                                                                        | Paragraph                                                  | Page                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------|

|         | A2A6 Data Input Code and Memory Counter A2A7 Recirculating Memory AN/FYC-12 Receiver A2A8 Level Converter A2A9 RCVR Data Processor A2A10 RCVR Control Logic A2A11 ARQ and Sync Control | 4-14g<br>4-14h<br>4-15<br>4-15a<br>4-15b<br>4-15c<br>4-15d | 4-99<br>4-106<br>4-109<br>4-110<br>4-112<br>4-120 |

|         | CHAPTER 5                                                                                                                                                                              |                                                            |                                                   |

|         | PREVENTIVE MAINTENANCE                                                                                                                                                                 |                                                            |                                                   |

| I.      | PREVENTIVE MAINTENANCE PROCEDURE                                                                                                                                                       |                                                            |                                                   |

|         | General                                                                                                                                                                                | 5 - 1                                                      | 5 - 1                                             |

|         | Tools and Test Equipment                                                                                                                                                               | 5 - 2                                                      | 5 - 1                                             |

|         | Preventive Maintenance Schedule                                                                                                                                                        | 5 - 3                                                      | 5 - 1                                             |

|         | Maintenance Procedures                                                                                                                                                                 | 5-4                                                        | 5 - 2                                             |

|         | Power Supply Adjustments                                                                                                                                                               | 5 - 4 a                                                    | 5 - 2                                             |

|         | Cleaning                                                                                                                                                                               | 5 - 4 b                                                    | 5 - 2                                             |

| II.     | OPERATIONAL TESTS AND OPTIMUM PERFO                                                                                                                                                    | RMANCE                                                     |                                                   |

|         | Operational Tests                                                                                                                                                                      | 5 - 5                                                      | 5 - 3                                             |

|         | Readying                                                                                                                                                                               | 5 - 5 a                                                    | 5 - 3                                             |

|         | Synchronizing                                                                                                                                                                          | 5 - 5 k                                                    | 5 - 3                                             |

|         | Inhibit Test                                                                                                                                                                           | 5 - 5 c                                                    | 5 - 3                                             |

|         | Completing Operational Testing                                                                                                                                                         | 5 - 5 d                                                    | 5-3                                               |

|         | CHAPTER 6                                                                                                                                                                              |                                                            |                                                   |

|         | CORRECTIVE MAINTENANCE                                                                                                                                                                 |                                                            |                                                   |

|         | GENERAL                                                                                                                                                                                |                                                            |                                                   |

|         | Corrective Maintenance                                                                                                                                                                 | 6 - 1                                                      | 6 - 1                                             |

|         | Recommended Test Equipment                                                                                                                                                             | 6 - 2                                                      | 6 - 1                                             |

|         | Procedures                                                                                                                                                                             | 6-3                                                        | 6-1                                               |

|         | Circuit Card Assembly Substitutions                                                                                                                                                    | 6-3a                                                       | 6 - 1                                             |

|         | Circuit Card Assembly Substitutions Circuit Tracing                                                                                                                                    | 6 - 3 b                                                    | 6 - 2                                             |

|         | e e e e e e e e e e e e e e e e e e e                                                                                                                                                  | 6-3c                                                       | 6-3                                               |

|         | Integrated Circuit Modules                                                                                                                                                             | 6-3d                                                       | 6-3                                               |

|         | Circuit Card Assembly Repair                                                                                                                                                           | 6 - 4                                                      |                                                   |

|         | Signal Analysis Circuit Card Assembly A2A1 Data Sample                                                                                                                                 | 0 - 4                                                      | 6 - 3                                             |

|         | Generator                                                                                                                                                                              | 6-4a                                                       | 6 - 4                                             |

| Section_ |                                                                        | Paragraph          | <u>P</u> age   |

|----------|------------------------------------------------------------------------|--------------------|----------------|

|          | Circuit Card Assembly A2A2 Data Bit                                    |                    |                |

|          | Generator and Fast Clock                                               | 6 - 4 b            | 6 - 6          |

|          | Circuit Card Assembly A2A3 Transmitter<br>Timing and Inhibit Logic     | 6 - 4 c            | 6 - 8          |

|          | Circuit Card Assembly A2A4 Transmitter                                 | 0 . 0              | 0 0            |

|          | Sync and ARQ Control                                                   | 6 - 4 d            | 6 - 10         |

|          | Circuit Card Assembly A2A5 Constant Rati                               |                    | - 10           |

|          | Code Generator                                                         | 6 - 4 e            | 6 - 12         |

|          | Circuit Card Assembly A2A6 Data Input Co<br>and Memory Address Counter | 6 - 4 f            | 6-13           |

|          | Circuit Card Assembly A2A7 Memory and                                  |                    |                |

|          | Parity Logic                                                           | 6 - 4 g            | 6 - 15         |

|          | Circuit Card Assembly A2A8 Line Receive                                |                    | ( 1 (          |

|          | and Line Drivers Circuit Card Assembly A2A9 Receiver Dat               | 6 - 4 h            | 6-16           |

|          | Processor                                                              | a<br>6 - 4 i       | 6-18           |

|          | Circuit Card Assembly A2A10 Receiver                                   |                    |                |

|          | Control Logic                                                          | 6 - 4 j            | 6 - 20         |

|          | Circuit Card Assembly A2A11 Receiver                                   | 6 - 4 k            | 6 - 22         |

|          | ARQ and Sync Control                                                   | 0 - 4 K            | 0-22           |

|          | CHAPTER 7                                                              |                    |                |

|          | ILLUSTRATED PARTS BREAKDOWN                                            |                    |                |

| I        | INTRODUCTION                                                           |                    |                |

|          | General                                                                | 7 - 1              | 7 - 1          |

|          | Abbreviations                                                          | 7 - 1 a            | 7 - 1          |

|          | Part Numbers                                                           | 7 - 1 b            | 7 - 1          |

|          | Major Sections                                                         | 7 - 2              | 7-1            |

|          | Section I Introduction                                                 | 7 - 2 a            | 7-1            |

|          | Section II Group Assembly Parts List Section III Numerical Index       | 7 - 2 b<br>7 - 2 c | 7 - 1<br>7 - 2 |

|          | Section IV Reference Designation Index                                 |                    |                |

|          | Beetion 17 Reference Besignation index                                 | , 2 a              | , 0            |

| II       | GROUP ASSEMBLY PARTS LIST                                              |                    | 7 - 4          |

| III      | NUMERICAL INDEX                                                        |                    | 7-66           |

| IV       | REFERENCE DESIGNATION INDEX                                            |                    | 7-76           |

| APPENDIX | K                                                                      |                    |                |

# LIST OF ILLUSTRATIONS

| Figure             |                                                                                                             | Page           |

|--------------------|-------------------------------------------------------------------------------------------------------------|----------------|

| 1 - 1<br>1 - 2     | Digital Data Set AN/FYC-12<br>System Configuration                                                          | 1 - 0<br>1 - 2 |

| 1 - 3<br>1 - 4     | Chassis Assembly (Removed From Cabinet) Digital Data Set AN/FYC-12 (Rear View)                              | 1 - 4<br>1 - 5 |

| 2 - 1<br>2 - 2     | Digital <b>Data</b> Set <b>AN/FYC-12</b> Outline Drawing Level Converter Assembly                           | 2 - 3<br>2 - 8 |

| 2 - 3              | Inhibit Control Transfer Clock Generator Assembly A2A3                                                      | 2-10           |

| 2 - 4              | AN/FYC-12 Setup Controls                                                                                    | 2-12           |

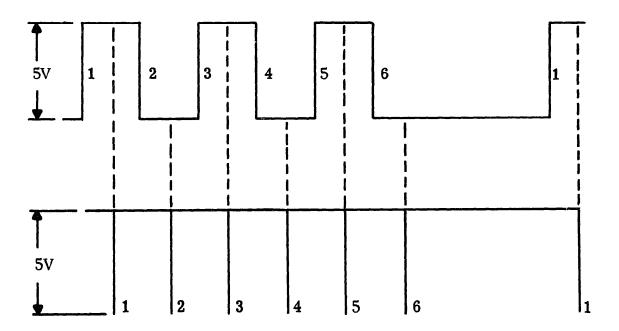

| 2 - 5              | Bit Stream Data Input                                                                                       | 2-17           |

| 2 - 6<br>2 - 7     | Transmitter Serial/Parallel Clock Correct Setting for Center Sample Switch                                  | 2-18<br>2-18   |

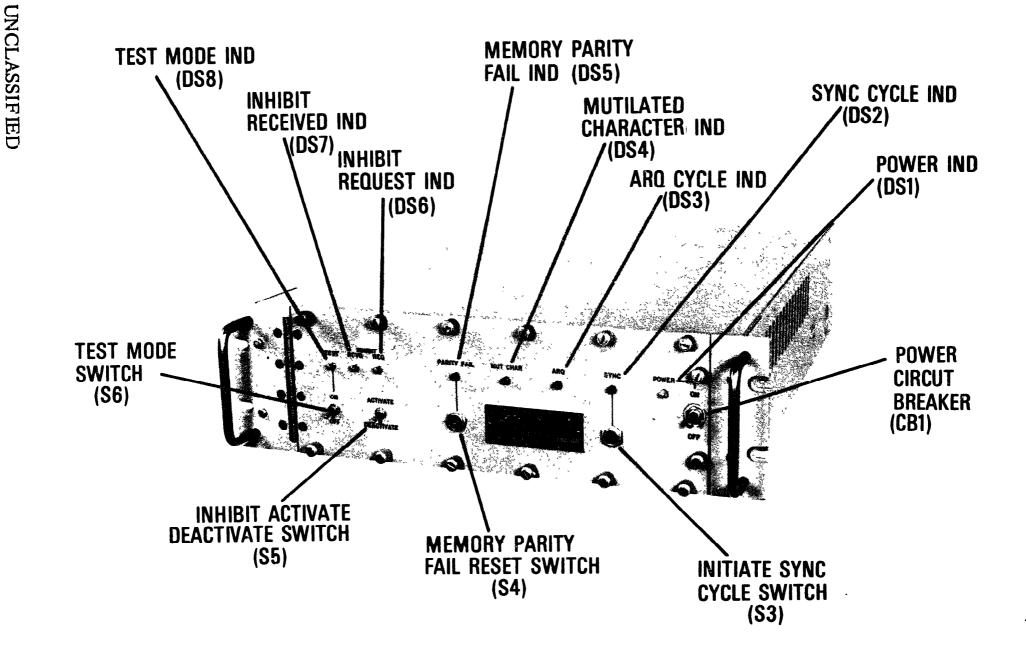

| 3-1                | AN/FYC-12 Operating Controls and Indicators                                                                 | 3 - 5          |

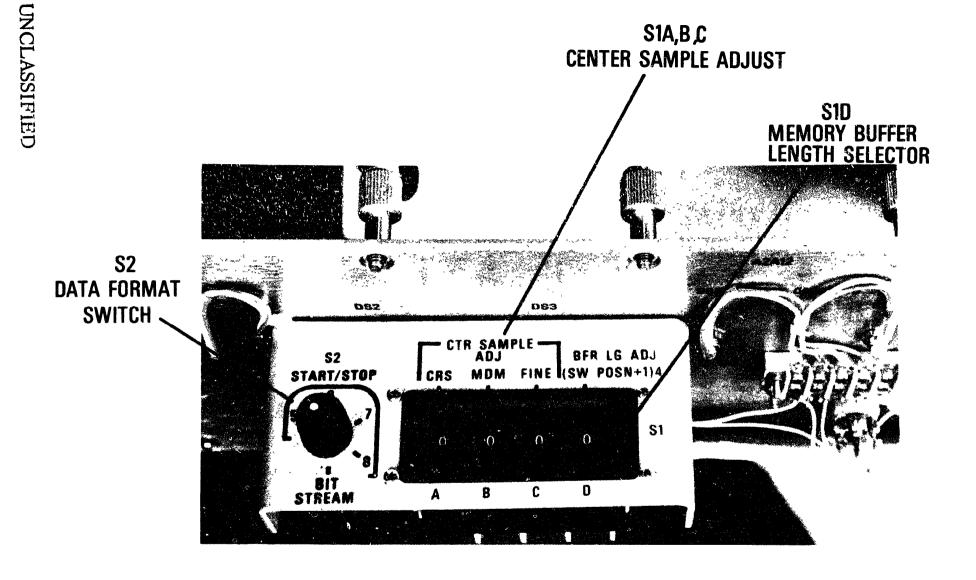

| 3 - 2              | AN/FYC-12 Operating Controls and Indicators  AN/FYC-12 Setup Controls                                       | 3-6            |

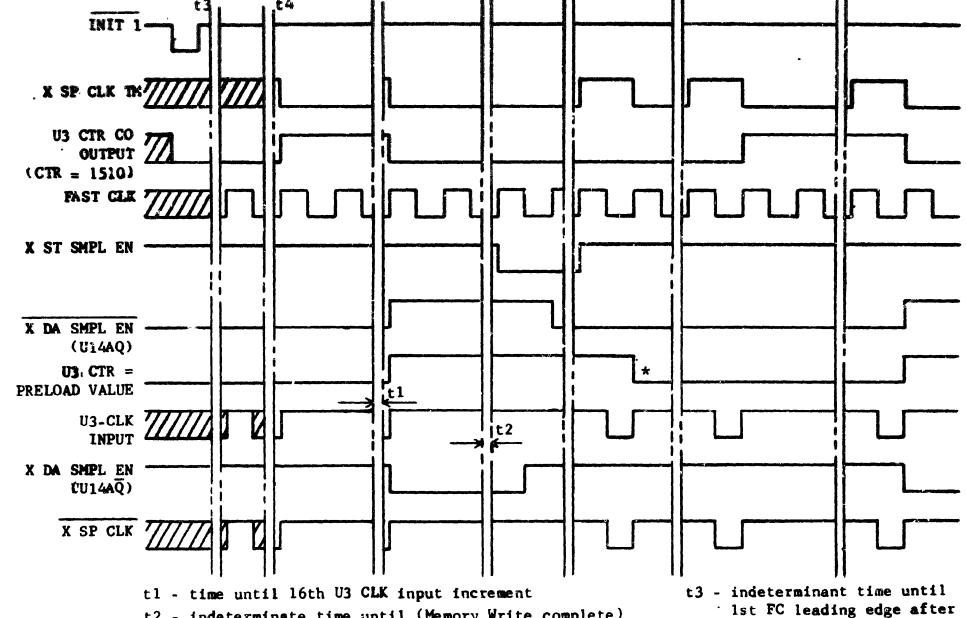

| 4 - 1              | Sample Enable Logic                                                                                         | 4-66           |

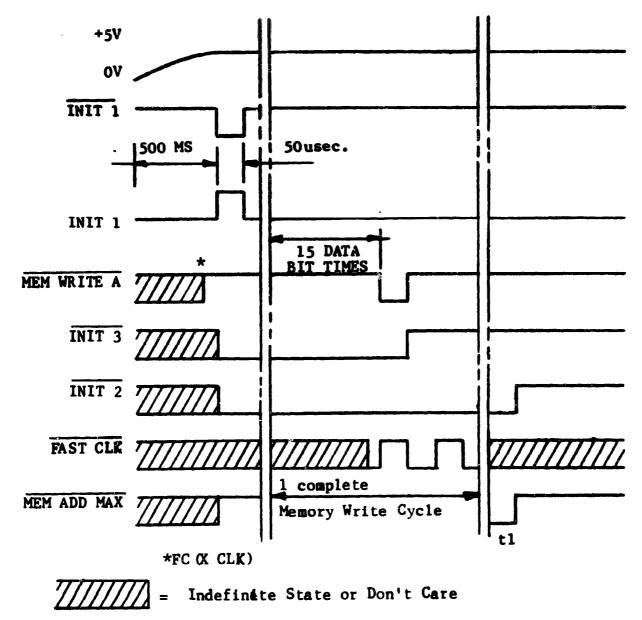

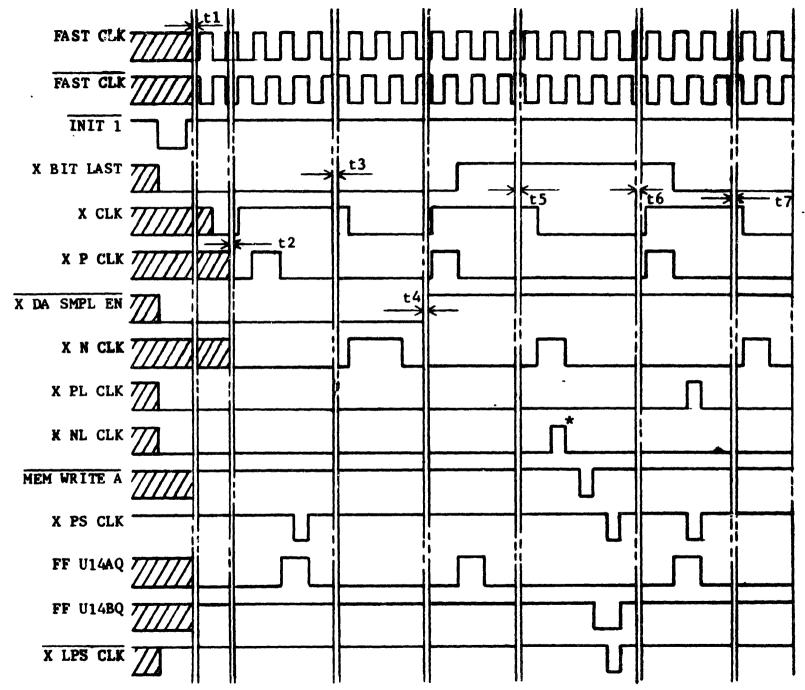

| 4 - 2              | Initialize Logic and Timing Diagram                                                                         | 4-68           |

| 4 - 3              | Sample Window - (Bit Stream)                                                                                | 4 - 70         |

| 4 - 4              | Sample Window - (Start/Stop)                                                                                | 4-71           |

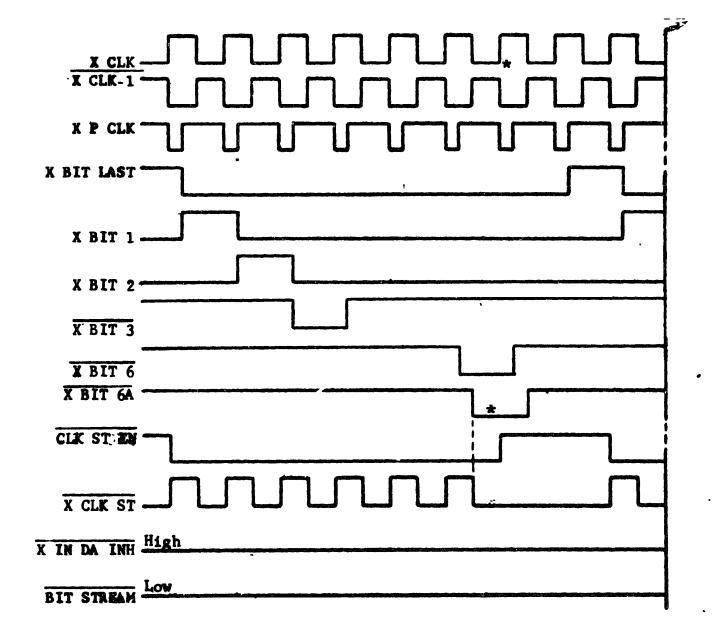

| 4 - 5              | XMTR Bit Counter Timing Diagram                                                                             | 4 - 72         |

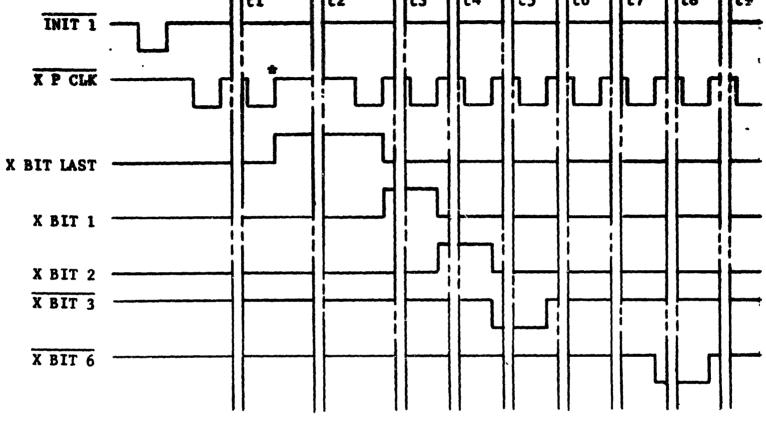

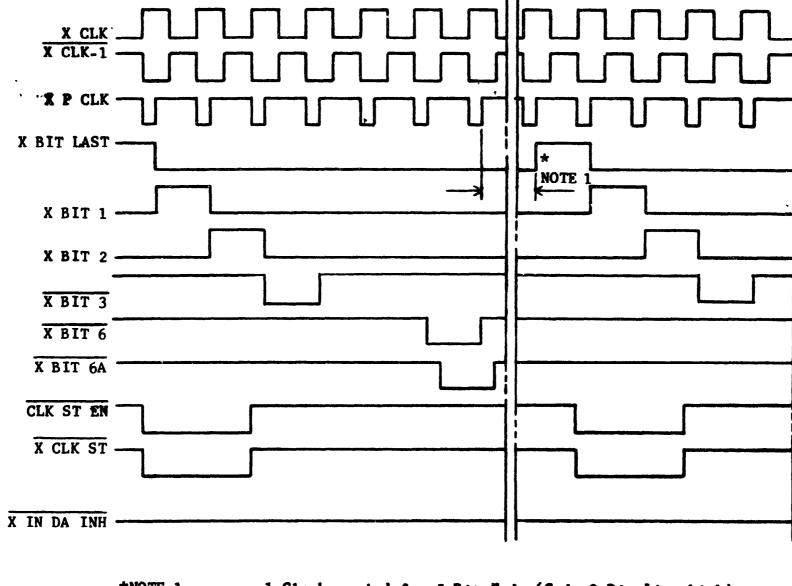

| 4 - 6              | Last Bit Counter Timing Diagram                                                                             | 4 - 7 4        |

| 4 - 7              | XMTR Bit 6A Gen Timing Diagram                                                                              | 4 - 7 5        |

| 4 - 8              | Clock Generator Timing Diagram                                                                              | 4 - 77         |

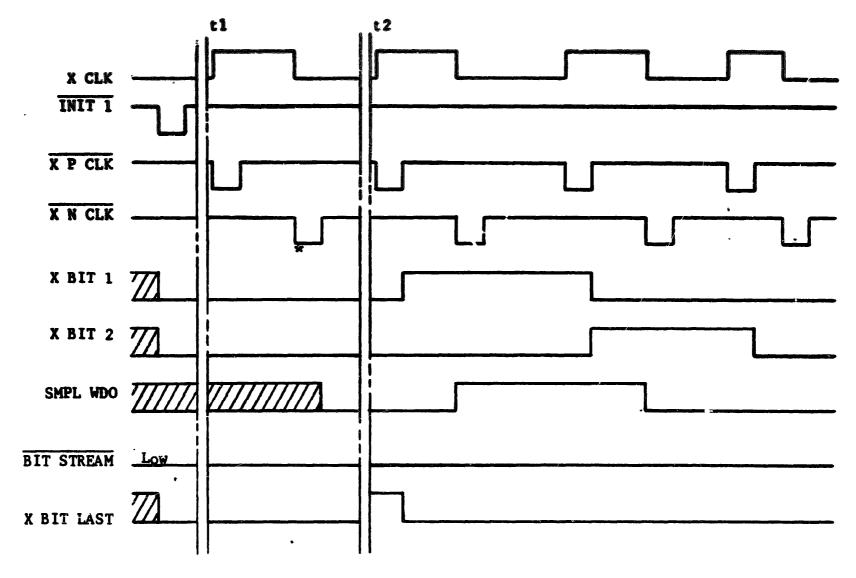

| 4 - 9              | Clock Step Generator - Bit Stream Mode Timing Diagram                                                       | 4 - 78         |

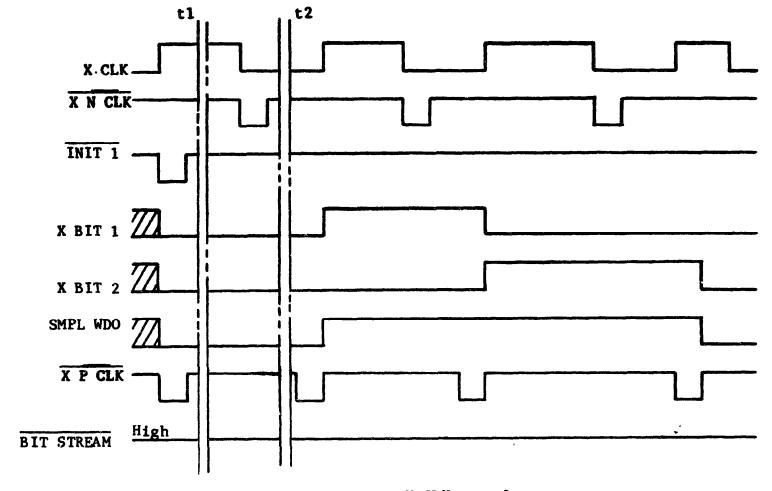

| 4 - 1 0<br>4 - 1 1 | Clock Step Generator - Start Stop Mode Timing Diagram<br>Memory Write Control and Parallel/Serial Clock Gen | 4 - 8 0        |

|                    | Timing Diagram                                                                                              | 4 - 8 2        |

| 4 - 12             | Inhibit Received Control Logic Timing Diagram                                                               | 4 - 8 3        |

| 4-13               | XMTR - ARQ Cycle Control Timing Diagram                                                                     | 4 - 8 8        |

| 4 - 1 4            | Sync Cycle Initiate Timing Diagram                                                                          | 4 - 9 0        |

| 4 - 1 5            | XMTR Sync Control Timing Diagram and Sync Cycle                                                             | 4-93           |

| 4 17               | Supervisor Control Timing Diagram  Sync Cycle Supervisor Control Timing Diagram                             | 4-96           |

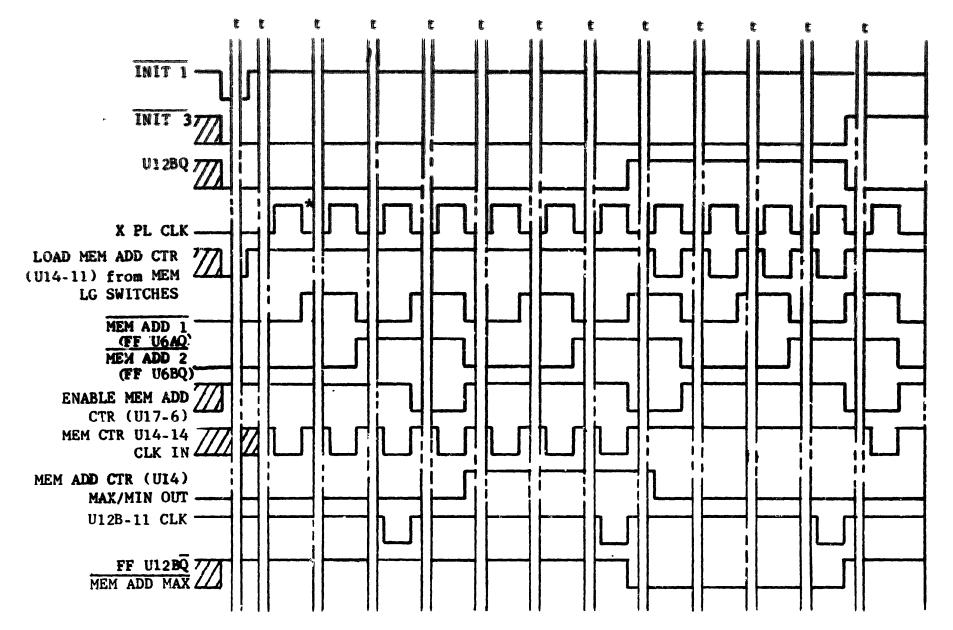

| 4 - 1 6<br>4 - 1 7 | Memory Address Counter Timing Diagram                                                                       | 4-105          |

| 5-1                | DC -DC Converter Test Points                                                                                | 5 - 2          |

| 7 - 1              | Digital Data Set AN/FYC-12                                                                                  | 7 - 6          |

| 7 - 1<br>7 - 2     | Electronic Equipment Cabinet Assembly A1                                                                    | 7 - 8          |

| 7 - 3              | Electronic Equipment Chassis Assembly A2                                                                    | 7 - 11         |

# LIST OF ILLUSTRATIONS, Continued

| Figure |                                                              | Page       |

|--------|--------------------------------------------------------------|------------|

| 7 - 4  | Circuit Assembly A2A1                                        | 7 - 17     |

| 7 - 5  | Circuit Card Assembly A2A2                                   | 7 - 20     |

| 7 - 6  | Circuit Card Assembly A2A3                                   | 7 - 23     |

| 7 - 7  | Circuit Card Assembly A2A4                                   | 7 - 26     |

| 7 - 8  | Circuit Card Assembly A2A5                                   | 7 - 29     |

| 7 - 9  | Circuit Card Assembly A2A6                                   | 7 - 32     |

| 7 - 10 | Circuit Card Assembly A2A7                                   | 7 - 3 5    |

| 7 - 11 | Circuit Card Assembly A2A8                                   | 7 - 38     |

| 7 - 12 | Circuit Card Assembly A2A9                                   | 7 - 40     |

| 7-13   | Circuit Card Assembly A2A10                                  | 7 - 43     |

| 7 - 14 | Circuit Card Assembly A2A11                                  | 7 - 4 6    |

| 7 - 15 | Front Panel Assembly A2A12                                   | 7 - 49     |

| 7-16   | Interface Assembly A2A14                                     | 7 - 5 2    |

| 7-17   | Back Plane Assembly A2A13                                    | 7 - 5 5    |

| 7 - 18 | Top Frame Assembly A2A15                                     | 7 - 5 7    |

| 7-19   | Electronic Chassis Assembly A2A16                            | 7 - 59     |

| 7 - 20 | DC -DC Converter Assembly A2A17                              | 7 - 61     |

| 7 - 21 | Rear Cover Assembly A3                                       | 7 - 63     |

| 7 - 22 | Extender Card Assembly TP1                                   | 7 - 6 5    |

| A -1   | Hex Inverters                                                | Αl         |

| A -2   | Quad 2 Input NAND Gate                                       | <b>A 2</b> |

| A -3   | Quad 2 Input NOR Gate                                        | A 3        |

| A -4   | Triple 3 Input NAND Gate                                     | A 4        |

| A - S  | Triple 3 Input NOR Gate                                      | A 5        |

| A -6   | Dual 4 Input NAND Gate                                       | A 6        |

| A -7   | Dual 4 Input NOR Gate                                        | A 7        |

| A -8   | 8 Input NAND Gate                                            | A 8        |

| A -9   | Dual 2-Wide 2-Input AND-OR Inverter Gates                    | A 9        |

| A - 10 | 4 Bit Magnitude Comparator                                   | A 10       |

| A-11   | 9 Bit Odd/Even Parity Generators/Checkers                    | A 1 1      |

| A - 12 | Dual Interface Transmitter                                   | A 1 2      |

| A-13   | Dual Interface Receiver                                      | A 1 3      |

| A-14   | Dual D-Type Flip Flop with Preset and Clear                  | A14        |

| A - 15 | Dual J-K Flip Flop with Clear                                | A 15       |

| A-16   | Dual J-K Flip Flop with Clear                                | A 16       |

| A - 17 | Dual J-K Flip Flop Clear, Preset, and Data Lockout           | A17        |

| A-18   | Synchronous 4 Bit Counters (Sheets 1 and 2)                  | A18        |

| A - 19 | Synchronous Up/Down Counter (Sheets 1 and 2)                 | A 2 0      |

| A - 20 | 4 Bit Parallel - Access Shift                                | A 2 2      |

| A -21  | 8 Bit Parallel - Out Serial Shift Registers (Sheets 1 and 2) | A 2 3      |

# LIST OF ILLUSTRATIONS, Continued

| Figure        |                                               | Page        |

|---------------|-----------------------------------------------|-------------|

| A - 22        | 256 Bit Read Write Memory                     | A 2 5       |

| A - 23        | 64 Bit Read/Write Memory                      | A 2 6       |

| A - 24        | 256 x 4 Bit Read Only Memory                  | A 2 7       |

| A - 2 4 A - E | ROM Programs                                  | A 28 - A 37 |

| A - 25        | Circuit Case Diagrams                         | A38         |

| A - 26        | Transmitter Block Diagram                     | A39         |

| A -27         | Receiver Block Diagram                        | A 4 0       |

| A -28         | Front Panel Block Diagram                     | A41         |

| A -29         | Assembly A2A1 Block Diagram                   | A42         |

| A - 30        | Assembly A2A2 Block Diagram                   | A43         |

| A -31         | Assembly A2A3 Block Diagram                   | A44         |

| A -32         | Assembly A2A4 Block Diagram                   | A45         |

| A - 33        | Assembly A2A5 Block Diagram                   | A46         |

| A -34         | Assembly A2A6 Block Diagram                   | A47         |

| A - 35        | Assembly A2A7 Block Diagram                   | A48         |

| A - 36        | Assembly A2A8 Block Diagram                   | A49         |

| A - 37        | Assembly A2A9 Block Diagram                   | A50         |

| A -38         | Assembly A2A10 Block Diagram                  | A 5 1       |

| A - 39        | Assembly A2A11 Block Diagram                  | A 5 2       |

| A -40         | Assembly A2A1 Logic Diagram                   | A53         |

| A - 41        | Assembly A2A2 Logic Diagram                   | A 5 4       |

| A - 42        | Assembly A2A3 Logic Diagram                   | A 5 5       |

| A - 43        | Assembly A2A4 Logic Diagram                   | A 5 6       |

| A -44         | Assembly A2A5 Logic Diagram                   | A 5 7       |

| A - 45        | Assembly A2A6 Logic Diagram                   | A 58        |

| A - 46        | Assembly A2A7 Logic Diagram                   | A 5 9       |

| A - 47        | Assembly A2A8 Logic Diagram                   | A60         |

| A -48         | Assembly A2A9 Logic Diagram                   | A 6 1       |

| A - 49        | Assembly A2A10 Logic Diagram                  | A62         |

| A-SO          | Assembly A2A11 Logic Diagram                  | A63         |

| A -51         | Front Panel Wiring Diagram                    | A 6 4       |

| A - 52        | Back Plane Wiring Diagram                     | A 6 5       |

| A - 53        | Initialization Sequence                       | A66         |

| A - 54        | ARQ Cycle Sequence                            | A67         |

| A - 5 5       | Synchronization Sequence                      | A68         |

| A - 5 6       | Transmitter Flow Diagram                      | A69         |

| A - 57        | Receiver Flow Diagram                         | A 7 0       |

| A - 58        | Test Point Locations                          | A71         |

| A - 59        | Transmitter 8 Bit Code Format Bit Timing      | A72         |

| A - 60        | Transmitter 8 Bit Code Format Bit Stream Data | A73         |

|               | Flow                                          |             |

# AN/FYC-12

# LIST OF ILLUSTRATIONS, Continued

| Figure |                                                            | Page  |

|--------|------------------------------------------------------------|-------|

| A -61  | Transmitter 8 Bit Code Format 5 Bit Start/Stop Data Flow   | A74   |

| A - 62 | Transmitter 11 Bit Code Format Bit Timing                  | A75   |

| A -63  | Transmitter 11 Bit Code Format 6 Bit Start/ Stop Data Flow | A76   |

| A -64  | Transmitter 11 Bit Code Format 8 Bit Start/Stop Data Flow  | A77   |

| A - 65 | Receiver 8 Bit Code Format Bit Timing                      | A78   |

| A -66  | Receiver 11 Bit Code Format Bit Timing                     | A79   |

| A -67  | Assembly A2A1 Wiring Diagram                               | A80   |

| A -68  | Assembly A2A2 Wiring Diagram                               | A81   |

| A -69  | Assembly A2A3 Wiring Diagram                               | A82   |

| A -70  | Assembly A2A4 Wiring Diagram                               | A83   |

| A - 71 | Assembly A2A5 Wiring Diagram                               | A84   |

| A -72  | Assembly A2A6 Wiring Diagram                               | A 8 5 |

| A-73   | Assembly A2A7 Wiring Diagram                               | A86   |

| A -74  | Assembly A2A8 Wiring Diagram                               | A87   |

| A - 75 | Assembly A2A9 Wiring Diagram                               | A88   |

| A -76  | Assembly A2A10 Wiring Diagram                              | A89   |

| A -77  | Assembly A2A11 Wiring Diagram                              | A90   |

# LIST OF TABLES

| Table |                                     | Page  |

|-------|-------------------------------------|-------|

| 1 - 1 | Equipment Supplied                  | 1-3   |

| 1 - 2 | Equipment Required But Not Supplied | 1-6   |

| 1 - 3 | Characteristics of the AN/FYC-12    | 1 - 7 |

| 1 - 4 | Electronic Chassis Assembly         | 1-13  |

| 2-1   | Power Interconnections              | 2 - 4 |

| 2 - 2 | Signal Interconnections             | 2 - 5 |

| 2 - 3 | Line Driver Capacitor Selection     | 2 - 9 |

| 2 - 4 | Memory Length Switch Setting        | 2-13  |

| 2 - 5 | Center Sampling Adjustment          | 2-16  |

| 3-1   | Controls and Indicators             | 3-1   |

| 4 - 1 | Supervisory Control Characters      | 4 - 4 |

| 4 - 2 | Bit Stream                          | 4 - 8 |

|       |                                     |       |

# LIST OF TABLES, Continued

| Table |                                         | Page    |

|-------|-----------------------------------------|---------|

| 4 - 3 | 5 Bit Start-Stop                        | 4-11    |

| 4 - 4 | 6 Bit Start-Stop                        | 4-13    |

| 4 - 5 | 7 Bit Start-Stop                        | 4-16    |

| 4 - 6 | 8 Bit Start-Stop                        | 4 - 20  |

| 4 - 7 | Unused Constant Ratio Codes             | 4-30    |

| 4 - 8 | 11 Bit Constant Ratio Unused Codes      | 4-31    |

| 4 - 9 | Sample Enable Counter Load              | 4 - 6 5 |

| 4-10  | Memorized Supervisory Characters        | 4-101   |

| 4-11  | Memory Length Control Signals           | 4-104   |

| 4-12  | Chip Select Decoder                     | 4-106   |

| 4-13  | Memory Switch Truth Table               | 4-131   |

| 5 - 1 | Test Equipment Required                 | 5 - 1   |

| 5 - 2 | Schedule of Preventive Maintenance      | 5 - 1   |

| 5-3   | DC -DC Converter Output Voltages        | 5 - 2   |

| 6-1   | Test Equipment Required For Maintenance | 6 - 1   |

| 6 - 2 | Transmitter Signal Name Glossary        | 6 - 25  |

| 6 - 3 | Receiver Signal Name Glossary           | 6 - 48  |

| 6 - 4 | Control Panel Signal Name Glossary      | 6-62    |

| 6 - 5 | Power Supply Signal Name Glossary       | 6-66    |

$Figure 1-1. \ Digital \ Data \ Set \ AN/FYC-12$

UNCLASSIFIED

#### CHAPTER 1

#### DESCRIPTION OF EQUIPMENT

#### I - CLASSIFICATION OF EQUIPMENT

1-1. CLASSIFICATION OF EQUIPMENT. -The Digital Data Set AN/FYC-12 and this manual are unclassified.

#### II - GENERAL DESCRIPTION

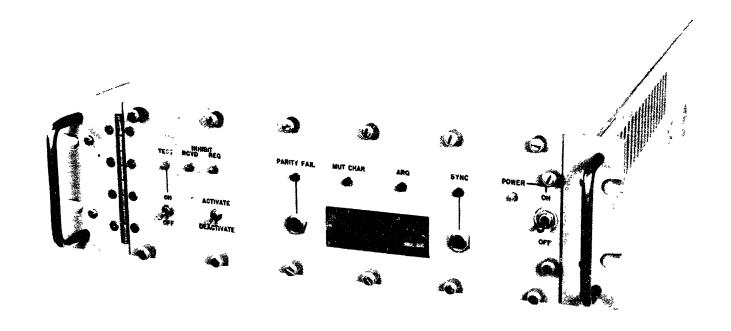

- 1-2. PURPOSE OF EQUIPMENT. This manual covers the operation and maintenance of the Digital Data Set AN/FYC-12, illustrated in Figure 1-1. The equipment is used to detect and correct transmission errors in digital communications systems.

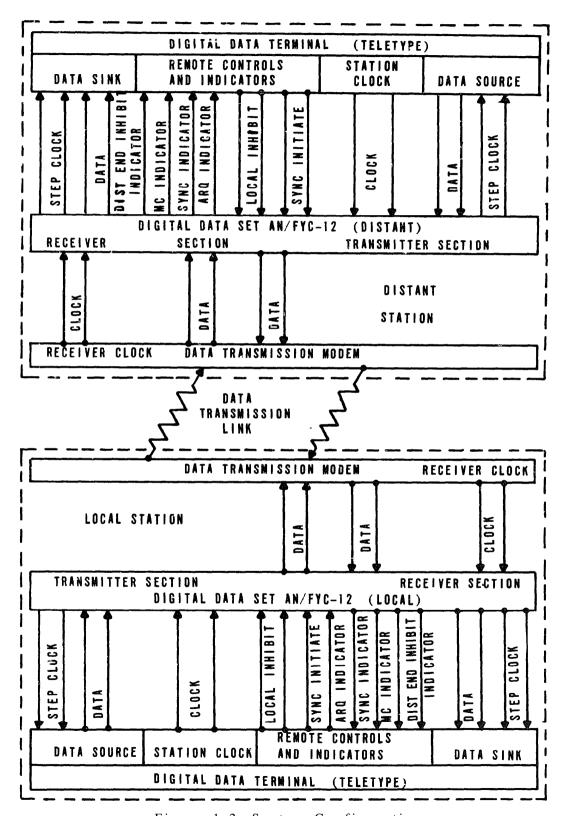

- 1-3. FUNCTIONAL DESCRIPTION. The Digital Data Set AN/FYC-12 functions as part of the Digital Data Telecommunications System. It operates in full duplex communication loops using start-s top or bit stream (continuous data) terminal equipment at transmission rates between 75 and 9600 baud. The AN/FYC-12, which is completely code transparent in all modes of operation, must have control of the data source with a clock step-character (startstop) or clock step/bit (bit stream). The output code to the data sink is identical to the input code from the data source. The terminal codes from the data source are encoded into constant ratio codes for transmission to a distant receiver, and stored in a cyclic TTL (Transistor -Transistor Logic) memory of adjustable length (maximum 64 characters). The input terminal code, not the constant ratio code, is stored. The distant receiver is able to distinguish non-constant ratio codes or unused codes from received communication (errors) and automatically request retransmission from the local transmission memory. This function is known as ARQ (Automatic Retransmission Request). The operator may resynchronize the system automatically or close down the distant transmitter (Inhibit Activate) by using supervisory characters. A typical system configuration (Figure 1-2) indicates that each Digital Data Set AN/FYC-12 consists of transmitter and receiver sections at the local and distant locations.

- a. System Operation. The local (AN/FYC-12) transmitter obtains data upon request from the local Digital Data Terminal (Teletype), stores it in a cyclic memory and encodes it into a constant ratio code before transmitting the data to the distant receiver. The distant (AN/FYC-12) receiver checks the incoming data and, if valid (constant ratio used code), decodes the constant ratio code to the original terminal code and outputs it to a distant data terminal (Teletype). The distant transmitter sends data from distant to local data terminals in the same manner. If invalid data (non-constant ratio or

Figure 1-2. System Configuration

unused code) is received, the receiver requests retransmission (ARQ) by raising a flag to the distant transmitter. The transmitter completes the active character, inhibits the distant data terminal for one memory cycle, then writes and transmits two ARQ supervisory characters followed by the contents of the transmitter memory. After a transmission &lay the local receiver detects the ARO supervisory characters and raises a flag to the local transmitter, which completes the active character, inhibits the local data terminal, and enters the ARQ cycle. Thus, the local and distant data terminals are closed down and both transmitters are sending from memory. The distant receiver receives the character that caused error as the first character after the distant source terminal inhibit has been removed, and rechecks it for validity. If a valid character is sent to the distant data terminal, both ends of the communication link leave the ARO cycle. The request for ARO can be from either receiver, so that data errors in each direction can be detected and corrected. No data is lost, added, or invali-&ted, but communications are closed down for one memory cycle so that extra time is required to complete transmission. If constant invalid data is received at either end, the system continues to repeat the ARQ cycle, closing down communications. (This results from a hardware fault or loss of synchronization between transmitter and receiver.) The operator may initiate "Sync Cycle", which re-synchronizes the system and probably alleviates the repeating ARQ cycle. If the synchronization has not moved by more than four bits backward or forward, no data will be lost, added, or invalidated from transmitted communication after repeated ARQ cycles and re-synchronization. The operator can control the distant transmitter with two supervisory characters. "Inhibit Activate" closes down or lights the "Inhibit Request" indicator (strap option) and "Inhibit Deactivate" opens data communications. See paragraph 4-4 for complete details of "ARO Cycle". "Sync Cycle", "Inhibit Activate" and "Inhibit Deactivate."

- b. Summary of Capabilities. A summary of technical characteristics of Digital Data Set AN/FYC-12 appears in paragraph 1-7.

- 1-4. PHYSICAL DESCRIPTION. The Digital Data Set AN/FYC-12 consists of one unit. Physical dimensions are given in Table 1-1 Equipment Supplied.

**DIMENSIONS** WEIGHT QUAN. FIG. **ITEM** (inches) (lbs) REF. W H D (uncrated) 1 AN/FYC-12 1-1 51/419 24\* 56

Table 1-1. Equipment Supplied

<sup>\*(</sup>overall depth including handles, 26)

The Digital Data Set AN/FYC-12 may be broken into two major assemblies: Al Steel cabinet and A2 Electronic chassis and card file.

a. Steel Cabinet Assembly A1. - The cabinet assembly is designed to minimize radio frequency interference and is equipped with eight knock-out holes 1-3/8 inches diameter in different positions for ease of interconnection cables which should run in a steel conduit. The battery power supply  $\pm 6V$  DC is connected to terminal board T-1 located on this assembly.

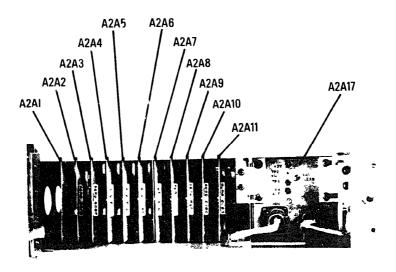

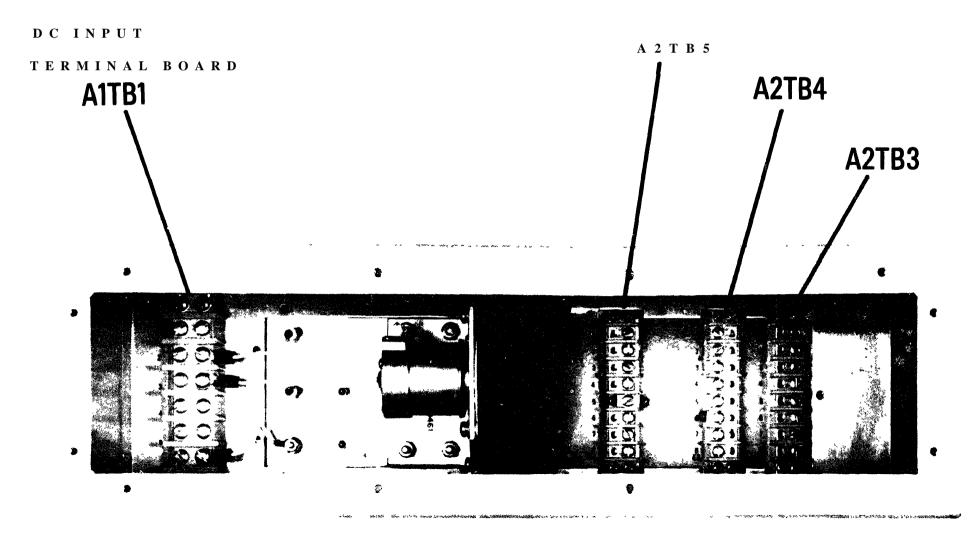

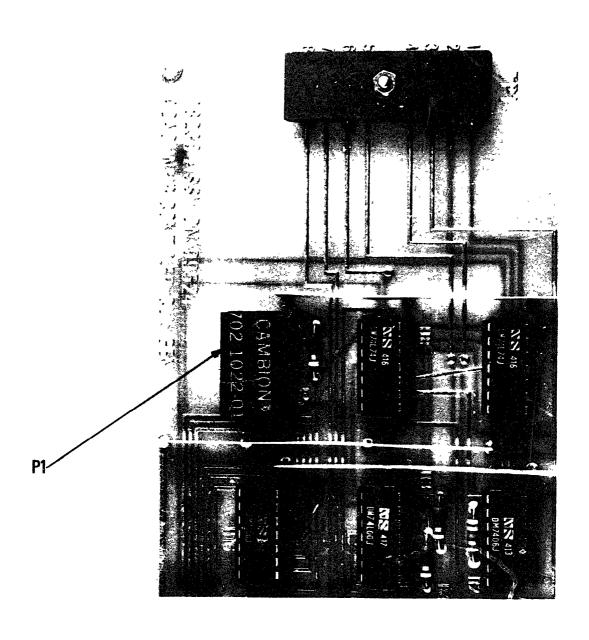

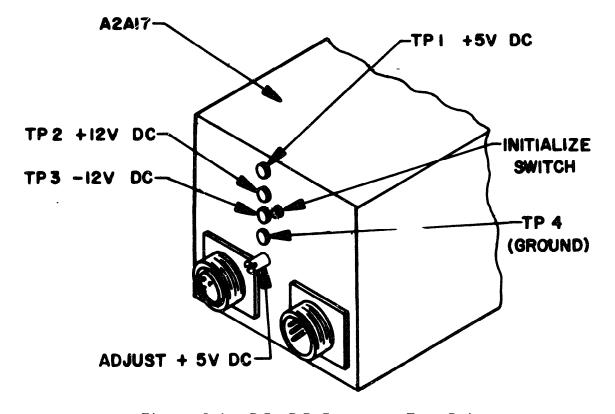

b. Electronic Chassis Assembly A2. - This sheet metal chassis with a hinged front panel is designed to compactly package (a) electronic circuit cards, (b) front panel indicators and controls, (c) set-up and initialize controls, and (d) DC-DC converter power supply. Figure 1-3 illustrates the chassis assembly removed from cabinet. The component assemblies of the chassis assembly are detailed in paragraph 1-7. Electronic circuit card assemblies A2A1 through A2A11 are designed to plug into a card file and can be removed easily, using the card extractor supplied with the unit. They are numbered consecutively from left to right. Assemblies A2A12, A2A13 and A2A14 are hard wired together by cable harness and are considered not removable from the electronic chassis assembly. The DC-DC converter (power supply) A2A17 is a completely sealed and non-repairable assembly. It can be readily removed by disconnecting connectors P1 and P2 and the mounting hardware. The converter package then slides out of the A2 chassis assembly easily. A rear view of Digital Data Set AN/FYC-12 with rear cover removed is shown in Figure 1-4. The interconnection terminal boards T-1 (battery power supply), TB-3, TB-4, and TB-5 (line signals) are clearly illustrated.

Figure 1-3. Chassis Assembly (Removed From Cabinet)

# SIGNAL TERMINAL BOARDS

Figure 1-4. Digital Data Set AN/FYC-12 (Rear View)

UNCLASSIFIED

1-5. EQUIPMENT REQUIRED BUT NOT SUPPLIED. - The following equipment is necessary but not supplied, to connect Digital Data Set AN/FYC-12 into the system:

Table 1-2. Equipment Required But Not Supplied

| QUANTITY | ITEM                                     |  |  |

|----------|------------------------------------------|--|--|

|          | Steel conduit 1-3/8 inches diameter      |  |  |

|          | Interconnecting cable (power and signal) |  |  |

|          | Electrician's Tool Kit                   |  |  |

For maintenance or troubleshooting the AN/FYC-12, the following **equip-**ment is required:

- 1. Extender card assembly (ON199640)

- 2. Integrated circuit test clip for 14 pin and 16 pin IC's

- 3. High quality oscilloscope, Tektronix 545B (or equivalent)

- 4. High quality test meter, Simpson 260 (or equivalent)

- 5. Digital pulse counter, H. P. 5245L (or equivalent)

#### III - QUICK REFERENCE DATA

- 1-6. EQUIPMENT IDENTIFICATION. Digital Data Set AN/FYC-12.

- 1-7. ELECTRICAL CHARACTERISTICS. Electrical characteris tics of the Digital Data Set AN/FYC-12 are as follows:

- 5. DC Input Power Required.

Voltage +6 Volts ±1V and -6 Volts ±1V or 12 Volts ±2 v

Current 6 Amps

Dissipation 72 Watts

b. Line Signals. - All line signals must meet MIL STD 188C for low level digital interface signals.

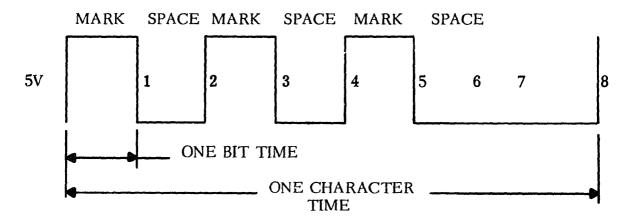

- c. Input Signals. Serial input data is at modulation rates between 75 and 9600 baud. An external system provides the station clock at two times the data rate. Remote control inputs for "Synchronization" and "Inhibit Activate" are +6V levels.

- d. Output Signals. Transmitter output is continuous data at modulation rates between 75 and 9600 baud, Data to local terminal (sink) are identical to input data from terminal (source). Local terminal (source) clock step is +6V for one bit time (bit stream) and two bit times (start-stop). Local terminal (sink) clock step is six cycles of receiver clock (bit stream) or +6V for one bit time (start-stop). The system provides four status or alarm conditions that are activated by +6V. They are:

- 1. Mutilated Character

- 2. ARQ Cycle

- 3. Sync Cycle

- 4. Distant End Inhibit

Table 1-3 tabulates additional electrical characteristics of the system, A list of the Electronic Chassis Assemblies is given in Table 1-4.

Table 1-3. Characteristics of the AN/FYC-12

#### SYSTEM

Data Rate - 75-9600 Baud (MIL STD 188C)

Station Clock - Twice Data Rate

Synchronization - Automatic After Manual Initiation

Number Channels - Single Channel Full Duplex

Line Interface - DC Low Level (MIL STD 188C)

#### TRANSMITTER

Input Data

Serial data in any of the following input

formats (MIL STD 188C):

1 - Bit Stream

2 - 5-Bit Start-Stop

3 - 6-Bit Start-Stop

## Table 1-3 (Continued)

- 4. 7-Bit Start-Stop

- 5. 8-Bit Start-Stop

Output Data -

Serial data constant ratio codes output formats (MIL STD 188C):

- Bit Stream and 5 Bit Start-Stop input formats transmitted in eight bit constant ratio code

- 6,7-and 8-Bit Start-Stop input formats transmitted in 11 bit constant ratio code

Source Step Clock -

Step clock to data source in phase with the station clock. Low level DC interface (MIL STD 188C)

- Bit Stream input format has six periods (one bit accepted/period) of station clock for each output character.

- Start-Stop input formats have high level (+6V) for two periods of station clock for each output char acter.

Memory -

Solid state TTL memory adjustable in length between eight and 64 characters in four character steps. Parity bit added to memory to detect memory errors.

Input Bit Timing -

The data source is enabled by the source step clock, but the first data bit may be delayed as much as two bit times. In Start-Stop input modes, the start bit (always low) is used to measure the delay and, hence, center sample remainder of the character. If no start bit is detected during the first two bit times, the "Idle Supervisor"

#### Table 1-3 (Continued)

is transmitted. In the Bit Stream input mode there is no start bit, and &lay must be measured and the center sample switch adjusted with an oscilloscope before transmission can begin.

Cons tan t Ratio

The terminal data codes are encoded by the transmitter into "Constant Ratio Codes" (all characters have four l's). This type of code has redundancy and requires more data bits than the terminal data codes, but allows errors to be detected at the distant receiver. Two lengths of constant ratio codes are used:

- 1. Bit Stream 5-Bit Start-Stop } 8 Bits/Character

- 2. 6-Bit Start-Stop

7-Bit Start-Stop 11 Bits/Character

8-Bit Start-Stop}

Supervisory Characters - In addition to normal data transmission between the transmitter and the distant receiver, the transmitter can control the distant AN/FYC-12 with six supervisory characters that are used to control the communication system. The six supervisory characters are:

- 1. Idle

- 2. Inhibit Activate

- 3. Inhibit Deactivate

- 4. ARQ Request

- 5. Sync A

- 6. Sync B

Table 1-3 (Continued)

ARQ Cycle -

If the receiver has detected an error, it automatically requests a retransmission (ARQ). The transmitter adds two "ARQ" supervisory characters the memory and then repeat the contents of its memory. This results in both ends of the data link retransmitting from memory (ARQ) and is called "ARQ Cycle."

sync Cycle-

The receiver must be synchronized to the transmitter for data communication. A unique bit sequence, "Sync A" supervisory character followed by "Sync B" supervisory character, generates eight 1's, which are used by the receiver to obtain correct synchronization. After "Sync A" and "Sync B" are transmitted, supervisory characters "Inhibit Activate" or "Inhibit Deactivate" are used to check that correct synchronization has been achieved. Note that supervisory characters used during "Sync Cycle" are not stored in the memory.

Inhibit Activate -

The distant transmitter may be closed down or requested to close down-(strap option) with the "Inhibit Activate" supervisory character, and reopen data communications with the "Inhibit Deactivate" supervisory character. Note that the distanttransmitter is always sending valid constant ratio line codes. When inhibited, it repeatedly sends an "Inhibit Deactivate" supervisory character or "Inhibit Activate" supervisory character, depending upon the position of the Inhibit Switch.

TM 11-5895-821-14-1

UNCLASSIFIED AN/FYC-12

#### Table 1-3 (Continued)

Strap Option -

The transmitter inhibit control logic may operate in two ways, depending upon the "strap option" (reversible plug located on assembly A2A4).

It may -

- Automatically close down when an Inhibit Activate supervisory character is received from the distant end.

- 2. Light the "Inhibit Request" indicator on the front panel when an "Inhibit Activate" is received.

#### RECEIVER

Input Data -

Serial data/constant ratio codes. DC Low Level Interface (MIL STD 188C) in two formats:

- 1. 8-bit Constant Ratio (four l's)

- 2. 11-bit Constant Ratio (four 1's)

Receiver Clock -

External receiver clock at twice the data rate. The fall of the receiver clock is at the center of each received bit.

Output Data -

Serial data in any of the following switched formats (Start-Stop formats have start and stop bits added). Code: are identical to those accepted by the transmitter.

- 1. Bit Stream

- 2. 5-Bit Start-Stop

- 3. 6-Bit Start-Stop

- 4. 7-Bit Start-Stop

- 5. 8-Bit Start-Stop

#### Table 1-3 (Continued)

Sink Step Clock -

Step clock to data sink in phase with the receiver clock. Low level DC interface (MIL STD 188C).

- Bit Stream format has six periods of step clock per correct character received.

- 2. Start-Stop input formats have high level (+6V) for one period of receiver clock for each correct character received.

Mutilated Character -

If the receiver detects a character that does not have four 1's (not constant ratio code) or is unused in selected input format, the receiver declares the character mutilated in transmission, closes the data sink for one memory cycle, and requests retransmission ARQ.

Idle Supervisor -

The receiver outputs to the data sink a character that consists of all l's (no start bit) and the normal step clock (used only in Start-S top modes).

Test Mode -

In the test mode of operation the local transmitter is connected directly to the input of the local receiver. The transmitter and receiver clocks are also made common.

CAUTION. - When the AN/FYC-12 is placed in test mode an "ARQ Cycle" is forced, and input data is lost from future transmission.

The test mode is useful for single end setup and fault finding.

TM 11-5895-821-14-1

UNCLASSIFIED AN/FYC-12

Table 1-4. Electronic Chassis Assembly

| A 2 A 1   | DATA SAMPLE GEN ASSY        |

|-----------|-----------------------------|

| A 2 A 2   | FAST CLK STEP GEN ASSY      |

| A 2 A 3   | IN CONT XFR CLK GEN ASSY    |

| A 2 A 4   | XMTR SYNC AND ARQ CONT ASSY |

| A 2 A 5   | CONST R CODE GEN ASSY       |

| A 2 A 6   | DATA INP COD RAM CNTR ASSY  |

| A 2 A 7   | RECRC MEMORY ASSY           |

| A 2 A 8   | LEVEL CONVERTER ASSY        |

| A 2 A 9   | RCVR DATA PROCESSOR ASSY    |

| A 2 A 1 0 | RCVR CONT LOGIC ASSY        |

| A 2 A 1 1 | RCVR ARQ AND SYNC CONT ASSY |

| A 2 A 1 2 | FRONT PANEL ASSY            |

| A 2 A 1 3 | BACK PLANE ASSY             |

| A 2 A 1 4 | INTERFACE ASSY              |

| A 2 A 1 5 | TOP FRAME ASSY              |

| A 2 A 1 6 | CHASSIS ASSY                |

| A 2 A 1 7 | DC-DC CONVERTER ASSY        |

1-8. ENVIRONMENT. - Optimum ambient environmental conditions for the Digital Data Set are as follows:

| 1. Operating temperature     | $0^{\circ}C$ to $+50^{\circ}c$ |

|------------------------------|--------------------------------|

| 2. Non-operating temperature | -15°C to +75"C                 |

| 3. Heat dissipation          | 72 Watts                       |

| 4. Humidity                  | Up to 95% with                 |

|                              | condensation                   |

A N / F Y C - 12

#### CHAPTER 2

#### INSTALLATION

#### I - UNPACKING AND INSPECTION

- 2-1. PACKAGING DATA. The unpackaged weight of the Digital Data Set AN/FYC-12 is 56 pounds; the packaged weight is approximately 80 pounds. The crated unit measures 25 inches wide x 32 inches deep x 16 inches high.

- 2-2. UNPACKING. The Digital Data Set AN/FYC-12 is packed in a container prepared for overseas shipment in accordance with Level A of specification MIL-E-17555G and Level C for domestic shipment. Upon receipt of the unit, carefully unpack the unit near the area where the unit is to be installed. The area should be large enough to allow removal from the carton. No special equipment is required for unpacking. Unpack the unit according to the following procedure:

- 1. Cut the banding straps on the outer container.

- 2. Open the outer carton and remove the cushioning on top and sides.

- 3. Cut the barrier bag at the heat seal in the overseas package and remove the inner container.

- 4. Open the inner carton and remove the desiccant bags and the cushioning from the top and sides of the unit.

- 5. Remove the manual and the Digital Data Set AN/FYC-12.

- 6. Remove the protective sleeve from the front of the AN/FYC-12.

The shipping containers and packing materials may be retained for reshipment.

2-3. INSPECTION PROCEDURE. - When the AN/FYC-12 is free of the shipping container, inspect it for dents, cracks, and security of access panels. Inspect the front panel for broken indicators or switches. When inspection of the external surfaces is complete, unfasten the captive screws (14) on the front panel assembly and open the panel. Check the eleven circuit cards (A2A1 through A2A11) to be sure each is inserted in its respective connector. Check the DC-to-DC converter assembly A2A17 to be sure it is securely fastened in the unit, and that connectors P-1 and P-2 are tightly secured. After inspection is complete, close the front panel and secure the captive screws.

UNCLASSIFIED

2-4. DAMAGE REPORT. - It is important to report any damage discovered during the inspection outlined in paragraph 2-3. Follow the instructions issued by the custodial department or agency.

#### II - INSTALLATION PROCEDURE

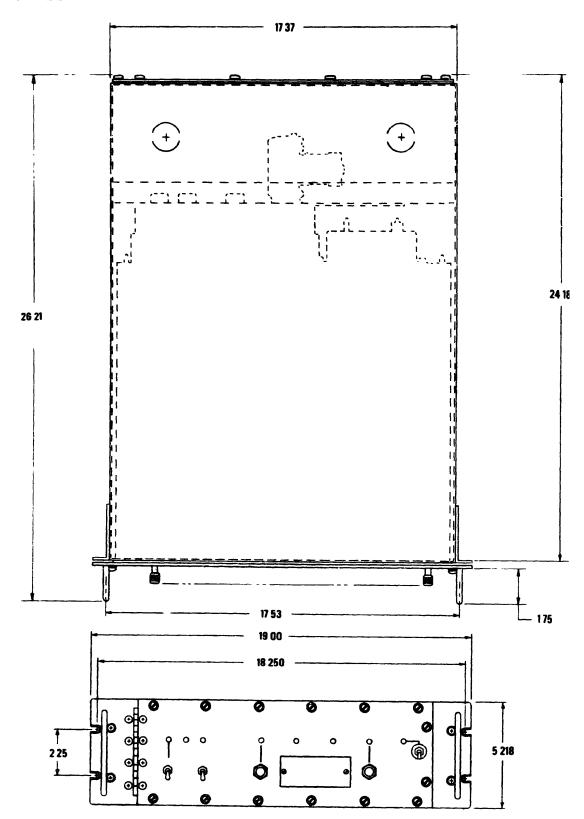

- 2-5. GENERAL. The Digital Data Set AN/FYC-12 is designed for installation in an RR-197 relay rack, or equivalent. It has four slotted holes through the front panel for mounting hardware and has eight 1-3/8 inch diameter knockouts, two each in the sides, top and bottom of the unit. Interconnections can be made through any of the openings. It is recommended that the power connections be made through a knock-out at the right side when viewing the unit from the front, and tie signal connections through a knock-out on the left side of the unit. These openings are designed to accept connectors for a 3/4 inch thin wall conduit. An outline drawing of the Digital Data Set AN/FYC-12 is shown in Figure 2-1.

- 2-6. TOOLS AND TEST EQUIPMENT. No special tools or test equipment are required during the installation and alignment of the equipment.

- 2-7. LOCATING THE EQUIPMENT. The Digital Data Set AN/FYC-12 should be located in an open slot of the RR-197 relay rack that has a minimum of 5-1/4 inch vertical clearance. The operating and non -operating environmental limitations are listed in paragraph 1-8. Access to the rear panel is necessary during installation. During normal operation access to the front panel only is required; however, in order to adequately ventilate the unit, the area to the rear and right sides should be clear of obstructions.

- 2-8. EQUIPMENT MOUNTING. Before installing the equipment, remove the rear cover. Punch out as many knock-outs as needed for cable entry. Select a knock-out on the right. top, bottom, or side of the unit (when viewed from the front) for the DC power cable and one on the left top, bottom, or side of tie unit for the signal cables. Place the AN/FYC-12 in the rack and install four 10-32 screws 1/2 inches long through the slotted holes in the front panel. After the unit is attached to the rack, the conduit for the interconnection wires should be installed. The power and signal cables should be physically separated as much as possible. Figure 1-4 is a rear view of the AN/FYC-12 showing the input and signal terminal board locations.

- 2-9. CABLE FABRICATION. Install the power cable in a cable entry tube and pull the cable through the rear access panel so that the input power terminations can be cut to size and the power cable fabricated outside the unit. A minimum of No. 14 gage insulated copper wire should be used for the input. power connections. After the harness has been fabricated, pull the input cable back through the cable entry tube, secure the cable, and connect the input connections in accordance with Table 2-1.

Figure 2-1. Digital Data Set AN/FYC-12 Outline Drawing

Table 2-1. Power Interconnections

Power Interconnection Cable to Terminal Board TB1 Located on Assembly A1. See Figure 1-4. Terminal Terminal FromFunction Number Туре T B 1 - 1 \* Battery +6 Volt Input No. 8-32 Screw (Plus) Battery -6 Volt Input TB1-2\* No. 8-32 Screw (Minus) Battery 6 Volt Return TB1-6\*\* No. 8-32 Screw (Common)

Note: - Terminals 3, 4 and 5 on TBl are not used.

<sup>\*</sup>When DC power is provided by a 12-volt power supply, strap the grounded, or common side of the power supply, TB1-1 or TB1-2 as the case may be, to the equipment common terminal, TB1-6.

<sup>\*\*</sup>When DC power is provided by a positive and negative 6-volt power supply, connect the grounded, or common power supply terminal to the equipment common terminal, TB1-6.

a. Signal Cable, - Install the signal cable on the left side of the unit, and fabricate the cable outside the unit, The signal connections are made to terminal boards TB-3, TB-4 and TB-5 of A2. Use six twisted shielded pairs for the external inputs. The shields on the six twisted pairs should be connected together and a ground lead connected to a ground lug located under TB-3 mounting screw. Use eight twisted shielded pairs for the outputs to the external system. Terminal 4-6 is provided with a terminal solder lug. move the lug and solder the return wire of three of the twisted pairs to this lug. The shields of these three pairs should be connected together and a ground wire connected to a ground lug located under the TB-4 mounting screw. Terminal 5-4 is provided with two terminal lugs. Remove the lugs and solder three of the returns of the twisted pairs to one lug and two of the returns to the other lug. Tie the shields of the five pairs together and connect a ground wire to the lug located under TB-5 mounting screw. After the signal harness has been fabricated, pull the signal cable through the entry tube, secure the cable, and connect the input and output signal connections in accordance with Table 2-2.

AN/FYC-12

#### UNCLASSIFIED

Table 2-2. Signal Interconnections

Two signal interconnection cables are required:

- a) Input signals to terminal boards TB3 and TB4

- b) Output signals to terminal boards TB4 and TB5

Terminal boards TB3, TB4 and TB5 are all located on Assembly A2. See Figure 1-4.

| From                          | Function                    | Terminal<br>Number | Terminal<br>Type |

|-------------------------------|-----------------------------|--------------------|------------------|

| Data Terminal (Source)        | Input Data                  | ТВЗ-1              | No. 5-40 Screw   |

|                               | Data Return                 | ТВЗ-2              | No. 5-40 Screw   |

| Data Terminal (Station Clock) | Clock Return                | ТВЗ-3              | No. 5-40 Screw   |

|                               | Station Clock               | T B 3 - 4          | No. 5-40 Screw   |

| Communications<br>Modem       | Clock Return                | ТВЗ-5              | No. 5-40 Screw   |

|                               | Receiver Clock              | T B 3 - 6          | No. 5-40 Screw   |

| Communications<br>Modem       | Receiver Input<br>Data Line | ТВ 3 - 7           | No. 5-40 Screw   |

|                               | Data Return                 | T B 3 - 8          | No. 5-40 Screw   |

| Input Cable                   | Shielding                   | TB3 Ground         | No. 6 Ground Lug |

| Data Terminal (Control)       | Local Inhibit<br>Return     | T B 4 - 1          | No. 5-40 Screw   |

|                               | Local Inhibit               | T B 4 - 2          | No. 5-40 Screw   |

| Data Terminal (Control)       | Sync Initiate               | T B 4 - 3          | No. 5-40 Screw   |

|                               | Sync Initiate<br>Return     | T B 4 - 4          | No. 5-40 Screw   |

Table 2-2 (Continued)

| T o<br>Data Terminal    | Function ABO Indicator | Terminal<br>Number | Terminal Type    |

|-------------------------|------------------------|--------------------|------------------|

| (Control)               | ARQ Indicator Return   | T B 4 - 5          | No. 5-40 Screw   |

| Data Terminal (Control) | M. C. Indicator        | T B 4 - 7          | No. 5-40 Screw   |

|                         | Return                 | T B 4 - 6          | No. 5 Lug        |

| Data Terminal (Control) | Sync Indicator         | T B 4 - 8          | No. 5-40 Screw   |

|                         | Return                 | T B 4 - 6          | No. 5 Lug        |

| Output Cable            | Shielding              | TB4 Ground         | No. 6 Ground Lug |

| Communications<br>Modem | Send Line Data         | T B 5 - 1          | No. 5-40 Screw   |

|                         | Return                 | T B 5 - 4          | No. 5 Lug        |

| Data Terminal (Source)  | Source Step Clo        | ck TB5-2           | No. 5-40 Screw   |

|                         | Return                 | T B 5 - 4          | No. 5 Lug        |

| Data Terminal (Sink)    | Output Data            | T B 5 - 3          | No. 5-40 Screw   |

|                         | Data Return            | T B 5 - 4          | No. 5 Lug        |

| Data Terminal (Sink)    | Sink Step Clock        | ТВ5-5              | No. 5-40 Screw   |

|                         | Return                 | T B 5 - 4          | No. 5 Lug        |

Table 2-2 (Continued)

| То                      | Function                         | Terminal<br>Number | Terminal<br>Type |

|-------------------------|----------------------------------|--------------------|------------------|

| Data Terminal (Control) | Distant End<br>Inhibit Indicator | T B 5 - 6          | No. 5-40 Screw   |

|                         | Return                           | TB5 - 4            | No. 5 Lug        |

| Output Cable            | Shielding                        | TB5 Ground         | No. 6 Ground Lug |

Note: - Terminals 7 and 8 on TB5 are not used.

b. Check For Correct Connections. - After the power and signal inputs have been connected, check to see that the power and signal cable conductors have been connected to the appropriate terminal points within the AN/FYC-12. Install the rear cover to complete the installation procedure.

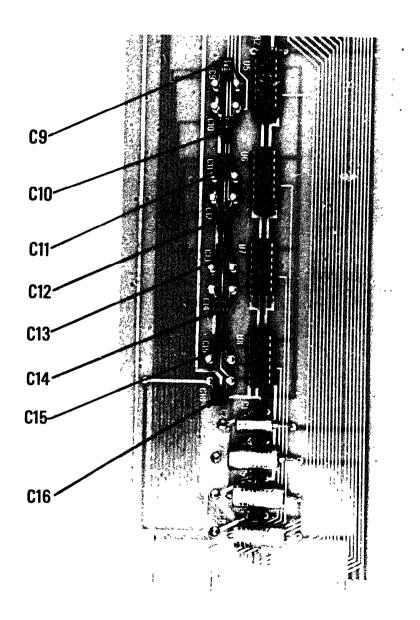

#### III - ADJUSTMENTS

2-10. LINE DRIVER CAPACITOR SELECTION. - The transmitter line driver capacitors installed in the equipment at the factory are selected to match low level DC interface specifications (MIL STD 188C) at the highest data rate (9600 baud). If the equipment is to be operated at a lower data rate then the line driver capacitors C-9 through C-16 on Assembly A2A8 must be changed in accordance with Table 2-3 to match (MIL STD 188C). The effect of the capacitors is to reduce the rate of change on the low level DC interface in order to minimize cross -talk and interference. Figure 1-3 shows the replaceable modules of the AN/FYC-12. Loosen the captive screws and open the front panel. Using the card extractor remove card assembly A2A8 (level converter assembly). Figure 2-2 shows the layout of the components; the eight line driver capacitors are mounted between terminals in the center of the card. Unsolder the eight capacitors and replace with values selected from Table 2-3. Once the capacitors have been installed, inspect to ensure that correct values were selected and good solder joints were made. Dress the capacitors to be below the height of IC's on the card and replace the A2A8 assembly in the AN/FYC-12. The equipment is now set to operate at the new baud rate, and the low level DC interface conforms to MIL STD 188C.

Figure 2-2. Level Converter Assembly A2A8

Table 2-3. Line Driver Capacitor Selection

|           | Capacitor Reference Numbers |               |              |                     |  |  |  |  |

|-----------|-----------------------------|---------------|--------------|---------------------|--|--|--|--|

|           | C10, C11, C12,              | C13, C14, C15 | C9 and C16   |                     |  |  |  |  |

| Data Rate | Value                       | MIL           | Value        | MIL                 |  |  |  |  |

| (Baud)    | Micro-Farads                | Designation   | Micro-Farads | Designation         |  |  |  |  |

| 75        | 0.82                        | CK06BX824K    | 0. 39        | CK06BX394K          |  |  |  |  |

| 150       | 0. 39                       | CK06BX394K    | 0. 22        | CK06BX <b>224</b> K |  |  |  |  |

| 300       | 0. 22                       | CK06BX224K    | 0. 10        | CK05BX104K          |  |  |  |  |

| 600       | 0. 10                       | CK05BX104K    | 0.047        | CK05BX473K          |  |  |  |  |

| 1200      | 0.047                       | CK05BX473K    | 0.022        | CK05BX <b>223</b> K |  |  |  |  |

| 2400      | 0.022                       | CK05BX 223K   | 0.010        | CK05BX103K          |  |  |  |  |

| 4800      | 0.010                       | CK05BX103K    | 0.0056       | CK05BX 562K         |  |  |  |  |

| 9600      | 0.0056                      | CK05BX 562K   | 0.0033       | CK05BX 332K         |  |  |  |  |

Note: - The AN/FYC-12 is equipped with capacitors to operate correctly at 9600 baud when unpacked from factory.

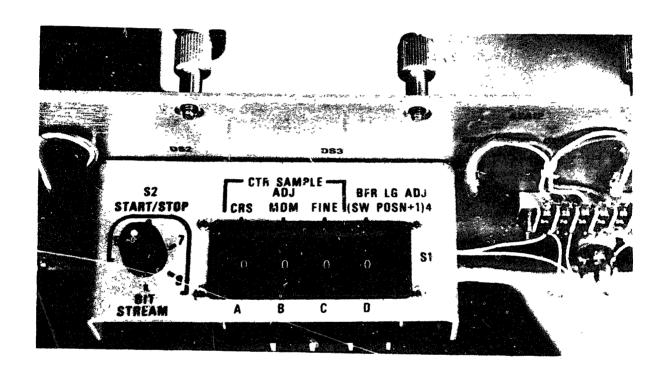

2-11. TRANSMIT INHIBIT OPTION. - The distant operator may request a close down of data communication by selecting "Inhibit Activate" (front panel switch). This sends the "Inhibit Activate" supervisory character which, &pending upon the strap option, is acted upon in one of two ways by the local AN/FYC-12. With option "A" selected in lights indicator "Inhibit RCVD" and, after completion of the character, automatically stops data communication. (The transmitter continues to send supervisory characters, which are not received by the distant sink terminal.) With option "B" selected, only the indicator "Inhibit RCVD" is lighted and the local operator must stop data communication manually. To re-open data communication, the distant operator must select "Inhibit Deactivate" on the front panel switch. This sends the "Inhibit Deactivate" supervisory character, extinguishes, the \*'Inhibit RCVD" indicator, and starts data communications again. Determine which option is to be utilized for system operation. Use the card extractor to remove card assembly A2A3 (Inhibit Control Transfer Clock Generator). Figure 2-3 shows the location of the components on this card assembly. The strap option (P1) is located at the lower front end of the card. option "A," pin 7 and pin 8 should be connected and pin 14 and pin 1 open.

Figure 2-3. Inhibit Control Transfer Clock Generator Assembly A2A3

A N / F Y C - 12

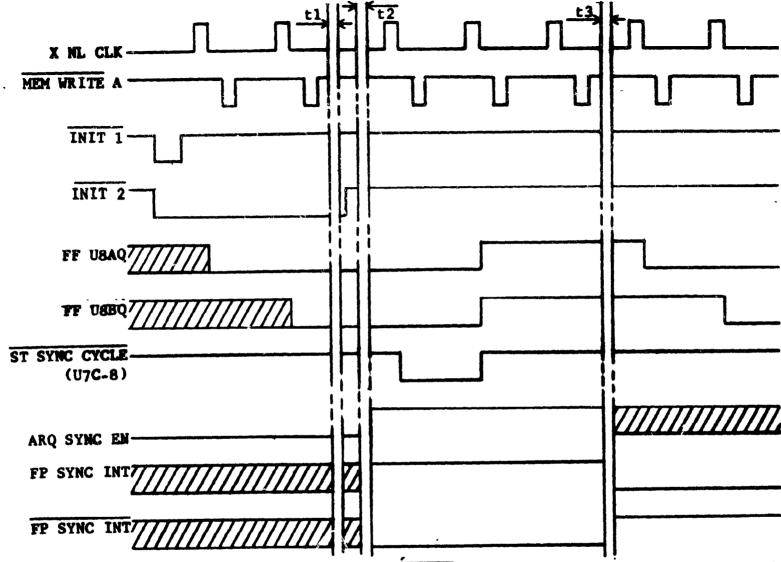

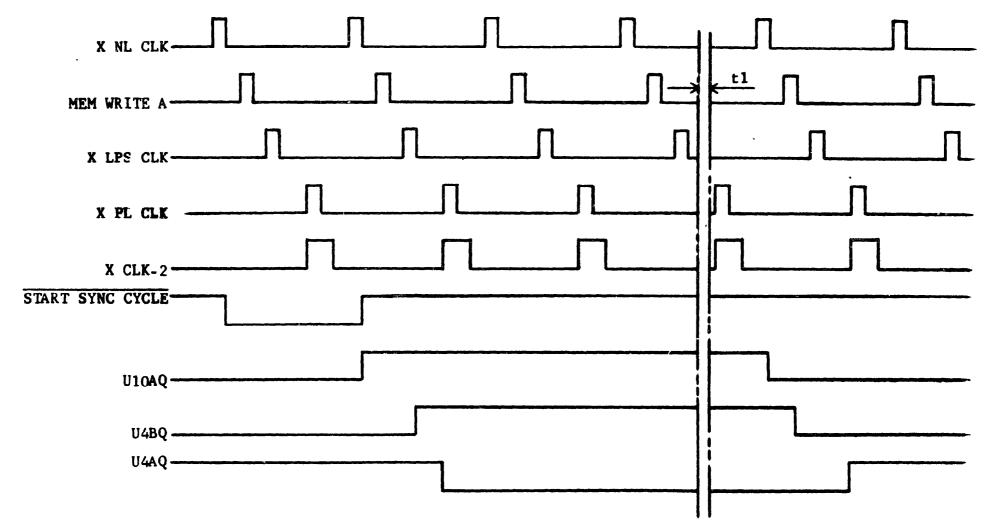

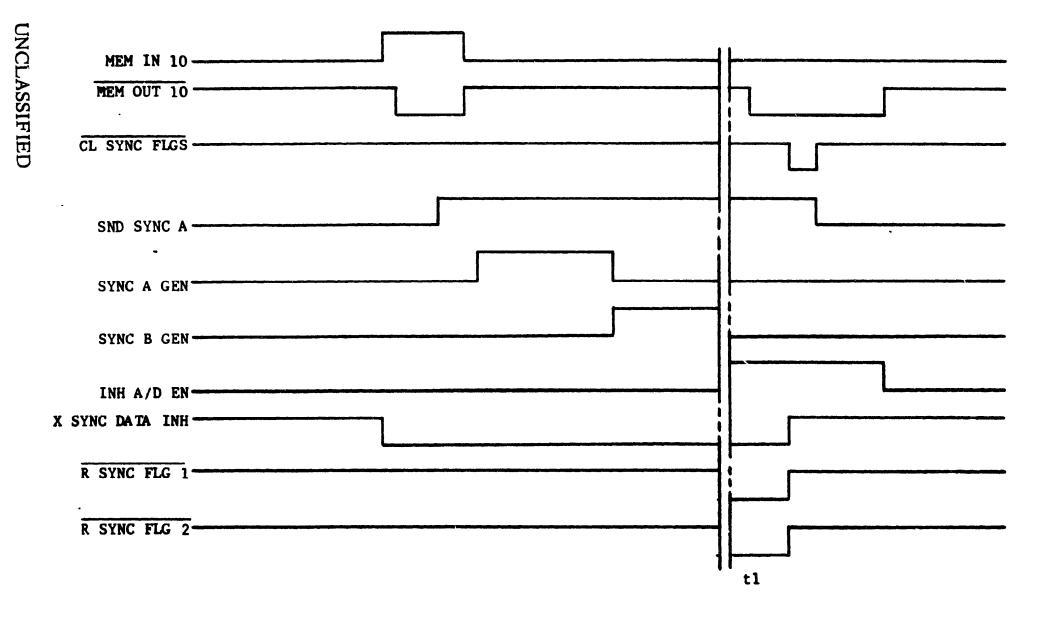

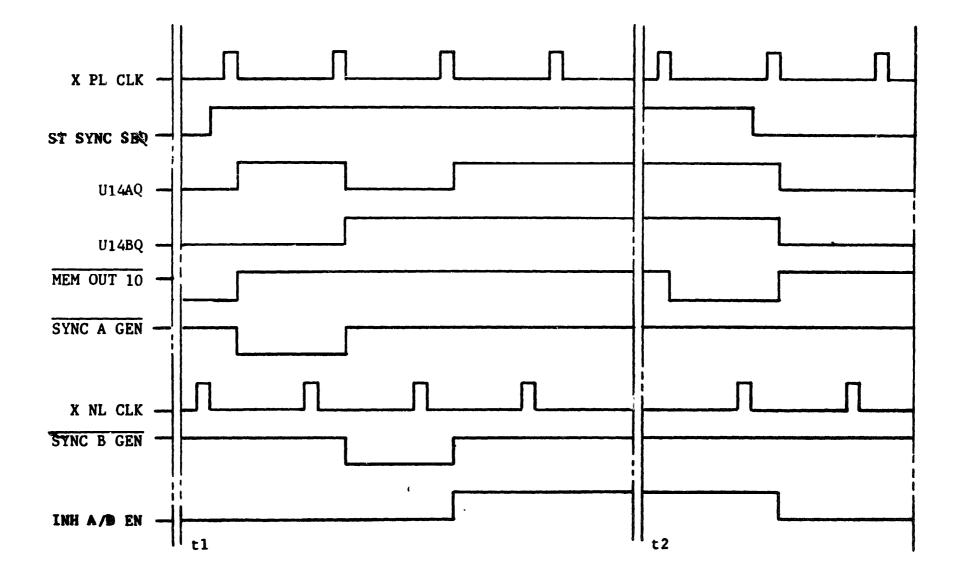

option "B" pin 14 and pin 1 are connected and pin 7 and pin 8 are open. Use the test meter to determine the option selected and reverse plug P1 to change the option if desired (reverse plug end to end). Make sure the plug is securely in its socket; then replace assembly A2A3. The transmit inhibit option is now set as required.